IMEC、全く新しいAIチップの情報を公開:機械学習アクセラレーターなど(1/2 ページ)

IMECはベルギーで開催された年次イベント「IMEC Technology Forum」でAI(人工知能)や機械学習に関連した新しい概念のチップに関する開発成果を公表した。

MRAM応用で機械学習向けアクセラレーターの消費電力低減

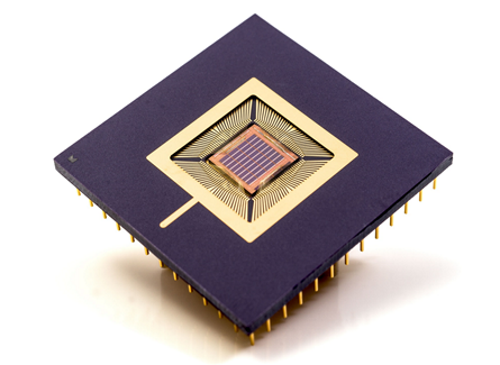

ベルギーの研究機関IMECがニューラルネットワークではなく磁気抵抗メモリセルのアレイを用いてコストと消費電力を低減した、機械学習向けアクセラレーターの詳細を明らかにした。初期の成果として、消費電力を2桁も低減するMRAMアレイが実現したという。

この大きな可能性を秘めた取り組みは、まだ始まったばかりである。IMECは2017年内に特許出願を予定しているが、それが済むまではこのチップのアーキテクチャや性能といった詳細を伏せておく方針だという。IMECはわずか18カ月前に、シリコンプロセス技術の主要な開発活動を拡張するという現行の取り組みの一環として、機械学習部門を立ち上げたばかりである。

IMECは、2017年5月16日から17日までベルギー・アントワープで開催された年次イベント「IMEC Technology Forum」の初日に行う数少ない発表の1つとして、このチップを披露した。それとは別に、研究者らは低消費電力の視線追跡システムと、義肢に新たなレベルの触感(ハプティクス)フィードバックをもたらす移植可能なチップの開発の進展についても発表した。

IMECのMRAMセルを用いたアレイは、1つのベンチマークに基づく自己学習分類タスクにおけるエネルギー効率を100倍に高めるという。IMECの半導体技術およびシステム部門で上級バイスプレジデントを務めるAn Steegen氏は「新たに実現したメモリを用いると、市場に出回るCMOSベースの機械学習アーキテクチャよりも、全体的にエネルギー効率を高めることができる」と述べた。

金属酸化物抵抗RAMをベースにしたセルアレイの応用も

IMECなどが「OxRAM」と呼ぶ、金属酸化物抵抗RAMをベースにしたセルのアレイが用いた別のチップも開発している。この65nmのチップは、40本の古典的なフルートのデータを取り込むことで、パターンの予測を学習する。そして、学習したパターンに基づいて、独自の音楽を創り出すという。

新たに実現したメモリの利点として、データビットを単一セルに保存できることが挙げられる。それにより、ダイサイズを可能な限り小さくすることができるという。この手法は、IMECにある期待を抱かせている。それは、将来的にモノのインターネット(IoT)のセンサーノード上にこのメモリを統合し、自己学習から恩恵を受けられるようにする、というものだ。

このチップを実際に役立たせるようにするには、数多くのアレイから成るヒエラルキー(=ピラミッド型階層組織)が必要である。IMECによると、チップ上のアレイのサイズについて明らかにする予定はないという。

同研究チームを率いる Praveen Raghavan氏は、「この自己学習チップの特長は、超高密度で(IBMのニューロシナプティックチップ『TrueNorth』よりも小さい)、消費電力が低く、量産可能なことだ」と説明している。

OxRAM のアプリケーション領域に使われている技術は、ニューラルネットワークではなく、連続したイベントを予測する「長期短期記憶(LSTM:Long-Short Term Memory)ネットワーク」に類似している。Raghavan氏は、「OxRAM は、LSTMアクセラレーターより安価だ。LSTMはより多くのデータとトレーニング用大型GPUが必要だ」と述べている。

OxRAMの手法は、敵対的生成ネットワーク(GAN: Generative Adversarial Network)のような用途に適している。GANは、ニューラルネットワークを相互に競わせることで学習速度を高める仕組みの新しい技術だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

IMECは、自己学習チップによって、コストと消費電力が制約されるIoTノードに機械学習能力をもたらすことを目指している 出典:IMEC

IMECは、自己学習チップによって、コストと消費電力が制約されるIoTノードに機械学習能力をもたらすことを目指している 出典:IMEC