モバイル端末向けパッケージング技術「FOWLP」(後編):福田昭のデバイス通信(112) TSMCが解説する最先端パッケージング技術(11)(1/2 ページ)

前回に引き続き、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」を取り上げる。今回はTSMCなど各社のFOWLPによるパッケージ開発事例を見ていく。

この記事は会員限定です。会員登録すると全てご覧いただけます。

TSMCが開発したFOWLP技術「InFO」

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回すなわち前編では、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程を解説した。後編である今回は、FOWLPによるパッケージの開発事例をご紹介する。

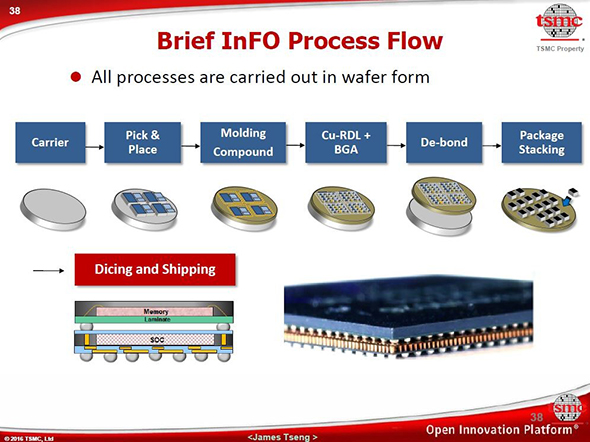

始めはTSMCが開発したFOWLP技術「InFO(Integrated Fan-Out WLP)」である。「InFO」は前編で説明した分類に沿うと、「チップファースト、フェースアップ」の製造工程で作られる。シリコンウエハーと同じ外形寸法のキャリアに、シリコンダイを置いていく。次に、キャリアの片面側全体をモールド樹脂で封止する。それからモールド樹脂の表面を削ってシリコンダイの回路面を露出させ、再構成配置配線層(RDL)を形成し、ハンダボールを載せる。そしてキャリアを外し、個々のパッケージに切断分離すれば、パッケージが完成する。ただし後述するPoPタイプの場合は、切断分離の前にスルーホールとバンプ搭載を実施し、パッケージ封止済みの半導体を載せておく。

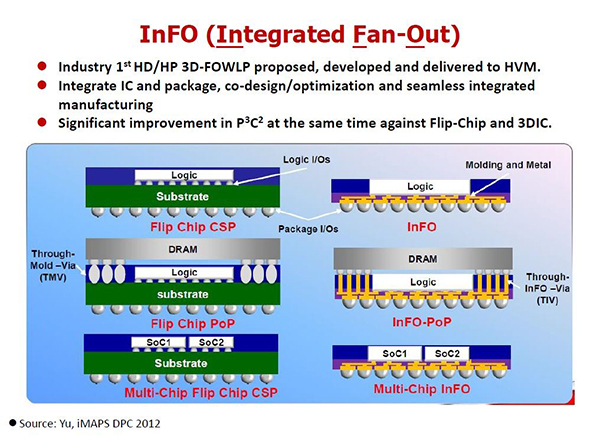

「InFO」の基本仕様は、再配置配線層(RDL)が3層で配線幅/間隔は2μm/2μm、ハンダボールのピッチが0.5mm、パッケージの厚みが0.45mm、パッケージの大きさが15mm角となっている。また「InFO」には、いくつかの派生品が存在する。パッケージ済み半導体デバイスを載せる、PoP(Package on Package)タイプの「InFO-PoP」、複数のシリコンダイを内蔵する「マルチチップInFO」などがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- メモリも中国が猛追 YMTCは新工場建設

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- SAIMEMORYの垂直ビルド構造メモリ開発がNEDO採択

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点