モバイル端末向けパッケージング技術「FOWLP」(前編):福田昭のデバイス通信(111) TSMCが解説する最先端パッケージング技術(10)(1/2 ページ)

ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の製造工程は、開発企業によって大きく異なる。そこで、いくつかに大別される製造工程の違いを紹介する。

この記事は会員限定です。会員登録すると全てご覧いただけます。

ウエハーレベルのファンアウトパッケージング技術

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、モバイル端末向けの最先端パッケージング技術に関する講演パートのあらすじを紹介するとともに、キーワード「ファンアウト」の意味を解説し、ウエハーレベルのファンアウトパッケージング技術「FOWLP(Fan Out Wafer Level Packaging)」の原形となる技術を説明した。今回からは、FOWLP技術に関する講演の概要を報告していく。

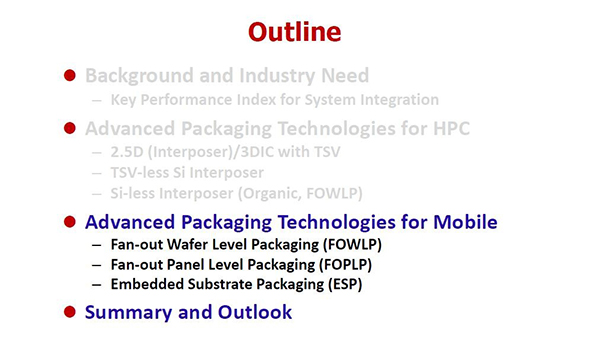

モバイル端末向けの最先端パッケージング技術。講演では3種類の技術を解説した。始めにウエハーレベルのファンアウトパッケージング(FOWLP:Fan Out Wafer Level Packaging)技術、次は、パネルレベルのファンアウトパッケージング(FOPLP:Fan Out Panel Level Packaging)技術、最後はプリント基板へ回路素子を埋め込むパッケージング(ESP:Embedded Substrate Packaging)技術である (クリックで拡大) 出典:TSMC

モバイル端末向けの最先端パッケージング技術。講演では3種類の技術を解説した。始めにウエハーレベルのファンアウトパッケージング(FOWLP:Fan Out Wafer Level Packaging)技術、次は、パネルレベルのファンアウトパッケージング(FOPLP:Fan Out Panel Level Packaging)技術、最後はプリント基板へ回路素子を埋め込むパッケージング(ESP:Embedded Substrate Packaging)技術である (クリックで拡大) 出典:TSMCFOWLP技術には、ファンアウト構造によって数多くの入出力数に対応するとともに、再配置配線構造(シリコンダイの入出力パッドからパッケージの入出力端子へと信号を引き回す高密度な多層配線の構造)を備えながらも樹脂基板を省いて材料コストを削減し、パッケージの外形をきわめて薄くしているという特徴がある。また製造プロセスがウエハーレベルでの処理なので、大量生産によってパッケージ1個当たりの製造コストをきわめて低くできる。

製造工程の違いがFOWLPの性能を大きく左右

前回の最後に説明したように、最初のFOWLP技術は半導体メーカーのInfineon Technologiesが2006年に開発したeWLB(embedded Wafer Level Ball grid array)技術である。その後、いくつもの半導体メーカーとパッケージ組み立て企業が、eWLB技術を改良したFOWLP技術を開発してきた。

FOWLP技術は、完成形であるパッケージの構造そのものは似ているのだが、製造工程は開発企業によってかなり違う。製造工程の違いが、完成形であるパッケージの性能を大きく左右する。

製造工程を大別すると、ウエハーレベルのキャリアを出発点として、最初にシリコンダイを載せるのか、あるいは最初に再配置配線構造を形成するのか、という違いがある。前者は「チップファースト(Chip-First)」、後者は「チップラスト(Chip-Last)」と呼ばれる。

さらに、シリコンダイをキャリアに載せるときに、回路面を上にするか、回路面を下にするか、の違いがある。前者は「フェースアップ(Face-Up)」、後者は「フェースダウン(Face-Down)」と呼ばれる。ただし「チップラスト」では、再配置配線構造を形成した後でシリコンダイを載せるので、必然的に「フェースダウン」となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ