二酸化ハフニウムを使った強誘電体トランジスタの研究開発(前編):福田昭のストレージ通信(76) 強誘電体メモリの再発見(20)(1/2 ページ)

今回から、「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)の研究開発状況を報告する。二酸化ハフニウム系強誘電体薄膜は、厚みがわずか7nm程度でも強誘電性を有することが確認されていて、このため、FeFETを微細化できることが大きな特長となっている。

隠されていた二酸化ハフニウムの強誘電体トランジスタ作製

前回では、従来型の強誘電体材料である、「ペロブスカイト系強誘電体材料」を使った強誘電体トランジスタ(FeFET:Ferroelectric FET)の研究開発の状況を説明した。今回からは、新材料である「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)の研究開発状況をご報告しよう。

本シリーズの第13回「強誘電体メモリの再発見(13)」では、2011年に国際学会でドイツの研究機関Fraunhofer Instituteを中心とする研究グループが、強誘電体の二酸化ハフニウム薄膜を作製したと発表したことが、正式な発見の公表だと述べた。ただしFraunhofer Instituteを中心とする研究グループは、2011年よりも数年ほど前には、強誘電体の二酸化ハフニウム薄膜の作製に成功していた。そして未公表の状態で、研究開発を続けていた。

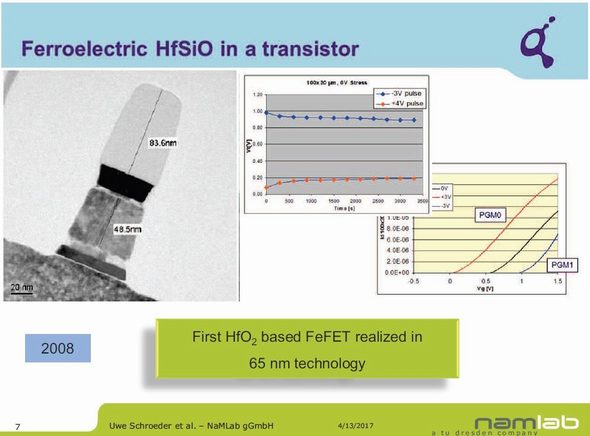

そのことを裏付ける資料がある。2017年5月に開催された「国際メモリワークショップ(IMW)」のショートコースでFraunhofer Instituteを中心とする研究グループは強誘電体メモリに関する技術解説の講演を実施した。その中で、二酸化ハフニウム薄膜をゲート絶縁膜に採用した強誘電体トランジスタの試作結果を示したのだ。

ショートコースで示された講演スライドによると、日付は2008年で、ドイツのDRAMメーカーであるQimonda(2009年に倒産)が65nmの製造技術で試作した。ゲート電極の厚みは83.6nm、二酸化ハフニウム薄膜(シリコン添加)の厚みは48.5nmである。この48.5nmという厚みは、従来型のペロブスカイト系強誘電体ではほぼ、実現不可能な薄さである。言い換えると、この程度にまで薄くできたからこそ、65nmと微細な加工技術が適用できた。ペロブスカイト系では、適用可能な加工技術は130nmにとどまっている。

試作した強誘電体トランジスタは、不揮発性メモリセルとして正常に動作した。初期の試作にもかかわらず、50分程度のデータ保持期間を実現している。ペロブスカイト系の強誘電体トランジスタが当初はデータの保持がうまくいかなかったという厳しい状況と比較すると、雲泥の差がある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増