二酸化ハフニウムを使った強誘電体トランジスタの研究開発(前編):福田昭のストレージ通信(76) 強誘電体メモリの再発見(20)(2/2 ページ)

極薄の二酸化ハフニウムがFeFETを一気に微細化

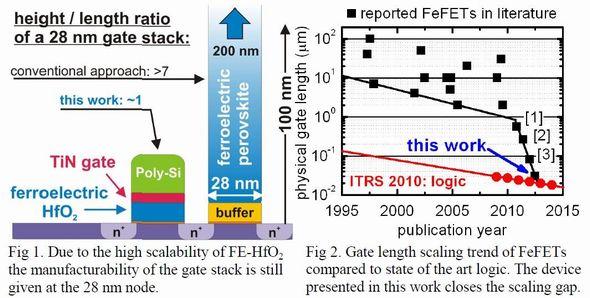

従来型のペロブスカイト系材料を使った強誘電体不揮発性メモリの微細加工寸法が130nmにとどまっている理由は、粗く言ってしまうと、薄くすると強誘電性が失われてしまうからである。約200nmが、ぎりぎりの厚みだといわれている。

半導体製造技術では、微細加工の寸法をアスペクト比が制限する。アスペクト比とは、加工対象の厚み(縦方向、あるいは垂直方向の寸法)と、加工寸法(横方向、水平方向、あるいはシリコンウエハー表面と平行な方向の寸法)の比率である。強誘電体を含む構造の場合、アスペクト比が「3」以上に増加すると、製造は相当に困難になる。強誘電体の厚みを200nmとすると、電極の厚みを加えて垂直方向の寸法は300nm程度になる。アスペクト比を3と仮定すると、加工寸法の限界は100nm前後である。

ところが二酸化ハフニウム系強誘電体薄膜は、厚みがわずか7nm程度でも、強誘電性を有することが確認されている。研究室レベルの値とはいえ、ペロブスカイト系に比べ、はるかに薄くできることは確実である。すなわち、はるかに微細な加工技術を適用できる。

2012年6月に開催された国際学会VLSIシンポジウムでは、Fraunhofer Instituteを中心とする研究グループが、二酸化ハフニウム(シリコン添加)を使った強誘電体トラジスタを28nm技術で試作してみせた。二酸化ハフニウムの厚さは、わずか9nmである。試作したトランジスタは不揮発性メモリとして動作し、104サイクルの書き換え寿命を有していた。

書き換えサイクル寿命そのものは、2011年に日本の産業技術総合研究所(産総研)がペロブスカイト系強誘電体トランジスタで実現した108サイクルにははるかにおよばない。ただし、産総研の試作したトランジスタはゲート長が260nmと大きい。Fraunhofer Instituteらの試作したトランジスタはゲート長が28nmと小さく、原理的には、非常に高い密度で不揮発性メモリを実現できる。

また強誘電体トランジスタにとって極めて重要な、強誘電体とシリコン基板の間にあるゲート絶縁膜は、MOSFETで一般的な二酸化シリコン(SiO2)である。しかもその厚みは1nmと非常に薄い。産総研がペロブスカイト系で試作したトランジスタのゲート絶縁膜は二酸化ハフニウムとアルミナの化合物材料であり、一般的なMOSFETで使われている材料ではない。

さらに、ゲート電極にはペロブスカイト系では高価な白金(Pt)を使っていたのが、二酸化ハフニウム系では安価な多結晶シリコンと窒化チタン(TiN)(厚みは8nm)の積層膜で済むことが明らかになった。このことも、二酸化ハフニウム系強誘電体トランジスタの将来性が有望視される理由となっている。

二酸化ハフニウム系強誘電体トランジスタ(FeFET)の構造(左)と、FeFETの物理寸法の推移(右)。左はペロブスカイト系FeFETと二酸化ハフニウム系FeFETで、アスペクト比の違いを示したもの。右は物理寸法の縮小化の推移を西暦年とともにグラフ化したもの。番号の1番と2番はペロブスカイト系材料、3番と今回の成果(this work)は二酸化ハフニウム系材料のFeFETである。出典:Fraunhofer Center Nanoelectronic Technologies、NaMLab、GLOBALFOUNDRIESが2012年6月のVLSIシンポジウムで共同発表した資料から(クリックで拡大)

二酸化ハフニウム系強誘電体トランジスタ(FeFET)の構造(左)と、FeFETの物理寸法の推移(右)。左はペロブスカイト系FeFETと二酸化ハフニウム系FeFETで、アスペクト比の違いを示したもの。右は物理寸法の縮小化の推移を西暦年とともにグラフ化したもの。番号の1番と2番はペロブスカイト系材料、3番と今回の成果(this work)は二酸化ハフニウム系材料のFeFETである。出典:Fraunhofer Center Nanoelectronic Technologies、NaMLab、GLOBALFOUNDRIESが2012年6月のVLSIシンポジウムで共同発表した資料から(クリックで拡大)(後編に続く)

⇒「福田昭のストレージ通信」バックナンバー一覧

関連記事

新材料「二酸化ハフニウム」を使った強誘電体メモリへの長い道

新材料「二酸化ハフニウム」を使った強誘電体メモリへの長い道

今回から2回にわたり、強誘電体の二酸化ハフニウムが、不揮発性メモリ用のキャパシターとしてどのような特性を示しているかを解説する。強誘電体不揮発性メモリ(FeRAM)のメモリセルで重要なのは、強誘電体キャパシターの特性だ。二酸化ハフニウムを絶縁膜とする強誘電体キャパシターが、優れた特性を備えているかどうかを調べる必要がある。 EUVの量産適用、半導体業界は前向きな見方

EUVの量産適用、半導体業界は前向きな見方

業界団体eBeam Initiativeの調査によると、EUV(極端紫外線)リソグラフィの実用化に対する業界の見方は、だいぶ前向きになっているようだ。 IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 FeRAMの長期信頼性に関する特徴

FeRAMの長期信頼性に関する特徴

強誘電体不揮発性メモリ(FeRAM)の長期信頼性を決めるのは、強誘電体キャパシターの分極特性だ。今回は、強誘電体キャパシターを劣化させる主な現象として「疲労(ファティーグ:fatigue)」と「インプリント(imprint)」について解説する。 NIMS、磁場のみで動作するトランジスタ開発

NIMS、磁場のみで動作するトランジスタ開発

物質・材料研究機構(NIMS)は、磁気でイオンを輸送するという、これまでとは異なる原理で動作するトランジスタを開発した。 産総研ら、STOを用いた人工ニューロンを開発

産総研ら、STOを用いた人工ニューロンを開発

産業技術総合研究所(産総研)の常木澄人研究員らによる研究グループは、スピントルク発振素子(STO)を用いた人工ニューロンを開発した。これを用いたニューロモロフィック回路音声認識システムの音声認識正答率は99.6%と高い。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増