“お蔵入りチップ”が掘り出し物に? Intel FPGAが示す過去の半導体の価値:この10年で起こったこと、次の10年で起こること(24)(1/3 ページ)

Intel FPGAとして発表された「Cyclone 10 LP」。これには、約10年前のプロセスとシリコンが使われている。これは、何を意味しているのだろうか。

買収から2年で、ようやく出せた“Intel FPGA”

IntelがFPGAメーカーAlteraを買収したのは2015年のことだ。その後しばらくはAlteraのロゴのまま、製品が販売されている。2017年になりようやく、Intelとして新しいFPGAをいくつか発表した。

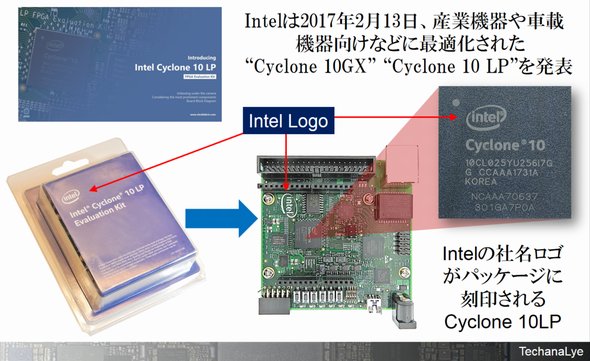

Intelが2017年に発表および発売したFPGAは、「Cyclone 10 GX」と「Cyclone 10 LP」。今回はCyclone 10 LPをメインに取り上げる。Intelは2017年2月、IoT(モノのインターネット)時代のエッジにもふさわしい、低消費電力かつ低コストのCyclone10 LPを発表した。2017年後半に日本でも発売されている。

図1にCyclone10 LPの梱包ケース、評価キット基板、チップパッケージを掲載する。先に述べたようにAlteraは買収後もAlteraロゴをパッケージにそのまま活用し続けた(パッケージを変えることは莫大な費用が発生する)。しかしCyclone 10 LPは、ボードにもチップのパッケージにも「Intel」のロゴが刻印されている。Alteraのロゴが消え、真に“Intel製品”として発売されたのだ。梱包ケース、基板、チップパッケージの全てがIntelと記載され、Alteraの面影はほとんどない。

買収から2年が経過してようやく、Intel一色で新しいFPGAを発売するに至ったわけだ。

60nmプロセスを用いる「Cyclone 10 LP」

Cyclone 10 LPは、最先端プロセスを用いず、約10年前の先端プロセスであった60nmを用いている。現在最先端の量産チップは10nmなので、おおよそ6倍(ゲート:トランジスタ形成部で6.0倍)ほど大きなパーツでできている。面積でいえば6x6=36となり、おおまかには30倍以上大きな面積となっているわけだ。逆に言えば、60nmを用いることで、単位面積当たりの集積度は、最新の10nmに比べると36分の1くらい低いものになってしまう。

Appleの公式発表によれば、同社の最新プロセッサ「A11 Bionic」は10nmで製造され、43億個ものトランジスタが搭載されている。A11 Bionicのチップ面積から、1mm2当たりのトランジスタ集積密度を計算すると、約4800万トランジスタ/mm2となる。だが、60nmではその30分の1程度、つまり160万トランジスタ/mm2しか集積できないことになる(他の数字も各所で語られているが、実装密度100%時の数字であるため、実際にはおおむね160万トランジスタよりもやや多くなる)。

A11 Bionicプロセッサを60nmで作ったと仮定してチップ面積を計算すると、2670mm2になる。つまり、52mm角の巨大なチップになってしまうのだ。実際にはこのような大きなチップを1チップ化することは製造上の問題でできないだろう。しかも、内部の配線長が長くなるので、その充放電の電力も巨大化してしまい、A11 Bionicの性能の半分程度も出せないものになると思われる。

Intelが2017年に発売したCyclone 10 LPは、上記のように最先端プロセスに比べて集積密度の低い(ロジックエレメント(LE)で最大12万個)FPGAとなっている。ちなみに、前世代のAltera「Cyclone V」では28nmプロセスを用いていて、最大30万1000個のLEを搭載している。

Cycloneシリーズは2002年に誕生し、2004年に「Cyclone II」、2007年に「Cyclone III」、2009年に「Cyclone IV」、2011年に「Cyclone V」と、製品名のカウントアップに伴い進化を続けてきた。現在、初代品とCyclone IIは、非奨励製品となっている。

製品名を1つずつカウントアップさせてきたことを考えると、Cyclone 10は、V(5)から一気に数字を上げたものになっているわけだ。実に、2倍である!!

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング