富士通のAIプロセッサ、演算精度とμアーキに工夫:競合より電力性能比10倍の向上(1/2 ページ)

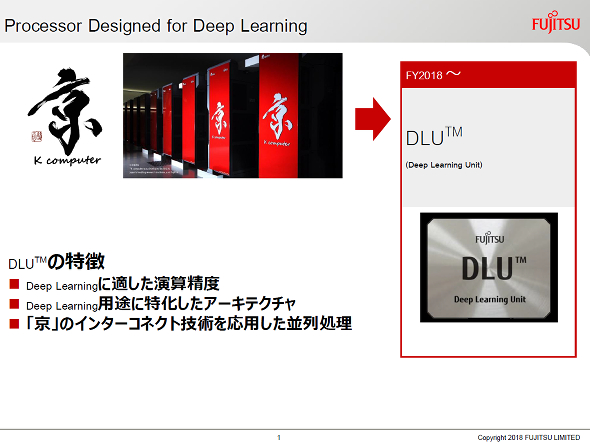

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ディープラーニング処理に特化したプロセッサ「DLU(Deep Learning Unit)」を展示した。競合となる既存のアクセラレーターと比較して、10倍の電力性能比を実現するとしている。

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ディープラーニング処理に特化したプロセッサ「DLU(Deep Learning Unit)」を展示した。競合となる既存のアクセラレーターと比較して、10倍の電力性能比を実現するとしている。

DLUは、ディープラーニングに適した独自開発の演算精度「DL-INT」に対応し、ディープラーニングに特化したアーキテクチャ、複数のDLUを接続するためのインターコネクトとしてスーパーコンピュータ(スパコン)京の「Tofu」を応用したネットワークを採用することが特長だ。

ディープラーニングに適した演算精度「DL-INT」の実装

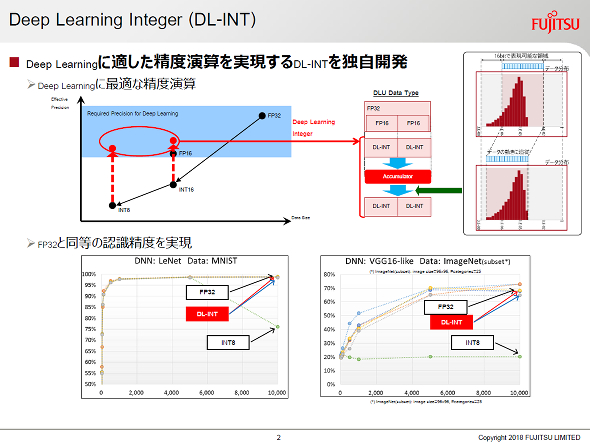

ディープラーニングの学習では一般的に、高精度実現のためFP32(32ビット浮動小数点)の演算精度で処理がなされる場合が多い。一方で、演算規模や消費電力削減のためFP16やINT16(16ビット整数)など、よりビット幅の小さな演算精度で学習が行われることもあるが、学習の失敗や過学習などにより推論精度の低下が発生することがあった。この問題に対し、GoogleやNVIDIA、Intelといったニューラルネットワーク処理に特化したプロセッサを開発するベンダーではそれぞれ独自の手法で改善を試みている。

富士通は、DL-INTを導入することでこの問題の解決を狙う。DL-INTは、INT8もしくはINT16などの整数形式をビット幅の広いアキュムレーターによって拡張し、データサイズを抑えつつ演算精度の向上を狙ったもの。さらに、演算中のデータを内部的に解析することで、データの精度変化に追従して小数点位置を自動的に制御し、演算精度の低下を防いでいる。これにより、FP32との比較で電力消費を低減しつつも、推論の認識精度をほぼ同等とすることができた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増