富士通のAIプロセッサ、演算精度とμアーキに工夫:競合より電力性能比10倍の向上(2/2 ページ)

ヘテロジニアスコアのアーキテクチャを採用

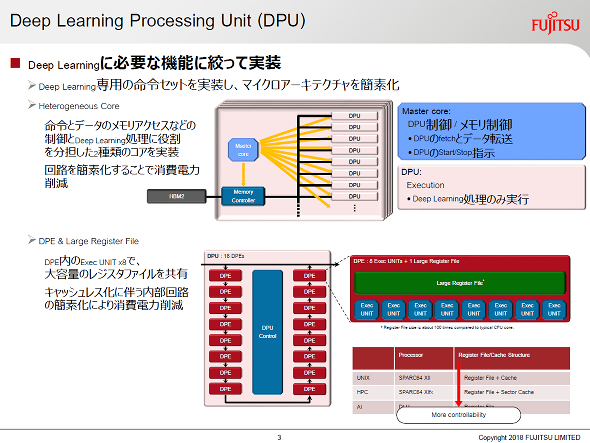

DLUは、ディープラーニング専用となるISA(命令セットアーキテクチャ)を採用し、ディープラーニング処理のみに特化した小規模な計算コア「DPU(Deep learning Processing Unit)」と、DPUやメモリの制御を行う「マスターコア」の2種類を実装するヘテロジニアスコアのマイクロアーキテクチャを採用する。1つのDLUは、数個のマスターコアと多数のDPUから構成されるイメージで、メモリコントローラーを介してHBM2メモリと接続する。

DPUは、16個の「DPE(Deep learning Processing Elemen)」から成り、さらにDPEは8個のSIMD演算器と一般的なCPUコアの100倍程度という大容量レジスタファイルを1つ持っている。ここで、DPEはキャッシュレス構造となるため、内部回路の簡素化による消費電力の削減や、ソフトウェア制御性の改善がなされたという。

マスターコアは、メモリ制御および、DPUに対してフェッチとデータ転送、処理の開始/終了指示を行う役目を持つ。このように、それぞれの処理に特化したコアを組み合わせることでマイクロアーキテクチャが簡素化し、電力性能比が改善するという。

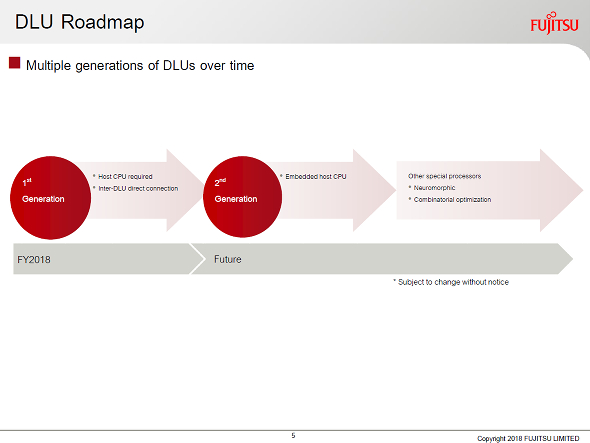

第1世代DLUの市場投入について、現時点では「チップの形で出すか、PCI Expressなどのインタフェースを持つ(既存サーバやコンピュータに後付け可能な)アクセラレーターカードの形で出すか未定」(同社担当者)とするが、リリース時期は2019年3月ごろを目標としている。

また、今後第2世代以降の開発についても示唆しており、第2世代以降ではホストCPUにDLUを組み込むことなどを予定している。

関連記事

ポスト京は高密度がカギ、富士通が試作チップを公開

ポスト京は高密度がカギ、富士通が試作チップを公開

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。 デンソー、自動運転の判断を担う新プロセッサ開発へ

デンソー、自動運転の判断を担う新プロセッサ開発へ

デンソーは2017年8月8日、自動運転システムに向けた新しいプロセッサを開発する子会社を設立すると発表した。CPUやGPUといったプロセッサとは異なる新しいプロセッサを開発し、半導体IPとして広くライセンス販売する計画。 Armの独壇場にはならない? AI向けコア市場

Armの独壇場にはならない? AI向けコア市場

CPUコアにおいて、多くの分野で高いシェアを誇るArmだが、AI(人工知能)エンジン向けチップのコアでは、独壇場とはいかないようだ。 GoogleのAI用チップ、Intelの性能を上回ると報告

GoogleのAI用チップ、Intelの性能を上回ると報告

Googleが2016年に発表した、機械学習の演算に特化したアクセラレータチップ「TPU(Tensor Processing Unit)」が、IntelのCPUやNVIDIAのGPUの性能を上回ったという。Googleが報告した。 Intel、“組み込みAIチップ”のPC搭載を狙う

Intel、“組み込みAIチップ”のPC搭載を狙う

Intelは、CPUの他に、Movidiusが手掛けてきたVPU(Vision Processing Unit)のような推論チップを、PCに搭載することを目指しているようだ。 Googleが「TPU 3.0」を発表、1ポッドで100PFLOPS

Googleが「TPU 3.0」を発表、1ポッドで100PFLOPS

Googleは、米国カリフォルニア州サンノゼで開催した開発者向け年次ベント「Google I/O」(2018年5月8〜10日)で、AI(人工知能)向けアクセラレータチップ「Tensor Processing Unit(TPU)」の新世代「TPU 3.0」を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待