NXPが新車載マイコン第1弾として800MHz、64MB品:安全走行制御向け(1/2 ページ)

NXP Semiconductorsは2018年6月19日、新しい車載用マイクロプロセッサ(MPU)/マイクロコントローラ(MCU)製品群「S32」の第1弾製品として、安全走行制御(セーフティ制御)システム向けのハイエンドMPU/MCU「S32S」を発表した。動作周波数800MHzのArm cortex-R52コアを8個と、最大64Mバイト(MB)の大容量フラッシュメモリを搭載するハイエンドMPU/MCUで、次世代の安全走行制御用途に向けるという。

NXP Semiconductorsは2018年6月19日、新しい車載用マイクロプロセッサ(MPU)/マイクロコントローラ(MCU)製品群「S32」の第1弾製品として、安全走行制御(セーフティ制御)システム向けのハイエンドMPU/MCU「S32S」を発表した。動作周波数800MHzのArm cortex-R52コアを8個と、最大64Mバイト(MB)の大容量フラッシュメモリを搭載するハイエンドMPU/MCUで、次世代の安全走行制御用途に向けるという。2018年10〜12月から一部顧客向けへのサンプル提供を開始し、量産は2019年以降の見込みだ。

性能10倍、ソフト再利用率90%、OTA対応、ASIL-D対応

NXPが「車載プロセッシング・プラットフォーム」と呼ぶS32は、これまで展開してきた旧Freescale Semiconductor製品を含む自動車向けMPU/MCU製品に代わる、新たなMPU/MCU製品群と位置付け、その製品コンセプトを2017年10月に発表していた(関連記事:NXPが車載用MCU/MPUを一新へ)。

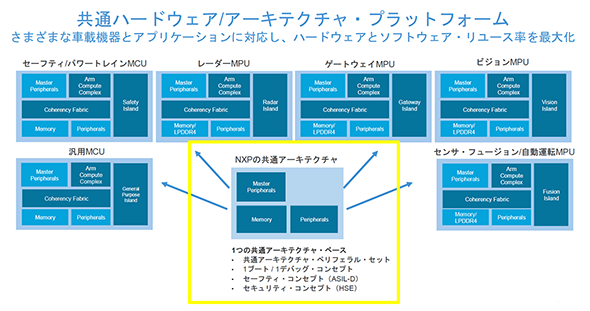

S32の開発コンセプトは、「自動運転」「電動化」「コネクティビティ」という現在の自動車業界におけるメガトレンドを実現するMPU/MCUで、メガトレンドの実現のため、現行の車載MPU/MCUに対し性能を10倍以上に高めるとした。また、性能向上、多機能化を受け自動車業界共通課題になっているソフトウェア開発負担の増大に対しても、従来よりもソフトウェア再利用性を高めたスケーラビリティを確保する仕組みを導入。ドメインと呼ぶ「機能別領域」内であれば、使用するMCU/MPUを置き換えてもソフトウェアの90%は再利用可能になるとする。またS32は、OTA(Over the Air)機能への対応、ASIL-D*1)対応といった高い安全性、セキュリティを実現する製品として展開するとしている。

*1)ASIL-D:自動車機能安全規格「ISO 26262」における安全性要求レベル。A〜Dまでの4段階があり、ASIL-Dが最も高い安全性要求レベルとなる。

「S32 車載プロセッシング・プラットフォーム」では、ドメイン共通のハードウェアをベースにしつつ、各ドメインでもハードウェアを共通化し、ソフトウェアの利用効率を高めている (クリックで拡大) 出典:NXPセミコンダクターズ

「S32 車載プロセッシング・プラットフォーム」では、ドメイン共通のハードウェアをベースにしつつ、各ドメインでもハードウェアを共通化し、ソフトウェアの利用効率を高めている (クリックで拡大) 出典:NXPセミコンダクターズ第1弾は安全走行制御システム向けハイエンド品

そのS32の第1弾製品が、安全走行制御システム向けのS32Sだ。S32Sが主にターゲットとするのが、安全走行制御システム領域の中でも、今後、高い成長率が見込まれる電気自動車(EV)/ハイブリッド車(HEV)特有の安全走行制御システムと、自動運転システム/先進運転支援システム(ADAS)だ。

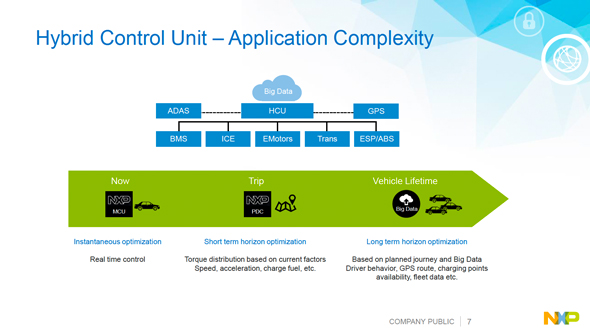

「例えば、HEVに搭載される、エンジンとモーターのトルク配分の制御を担う“ハイブリッド・コントロール・ユニット”は、これまでブレーキやアクセルの操作状況に応じて、トルク配分を決定してきた。しかし、次世代の自動車では、より効率的にエンジン/モーターを駆動させるため、路面状況や電池や燃料の残量などの要素を含めて、最適なトルク配分を決めたいというニーズが出ている。こうした処理を行うには現行のMCUでは、性能が足りず、より性能の高いMCUが求められている」とする。

そこでS32Sは、動作周波数が800MHzという安全走行制御システム向けMPU/MCUでは異例の高速動作を行うCPUコア「Arm Cortex-R52」を8個(ロックステップ動作*2)のため論理4コアとなる)を搭載した。「ハイブリッド・コントロール・ユニット向けの現行のMCU(MPC5744P)は、CPU2個(論理1コア)で動作周波数は200MHz。S32Sは、CPU個数で4倍、動作周波数も4倍であり、単純計算だが性能は16倍になった」とS32の開発コンセプトである「性能10倍」を達成したとする。

*2)ロックステップ動作:2個のCPUコアで同一の処理を行い冗長性を持たせる動作。ASIL-Dでは必須の機能とされる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増