埋め込みMRAMのメモリセルと製造プロセス:福田昭のストレージ通信(106) GFが語る埋め込みメモリと埋め込みMRAM(6)(1/2 ページ)

今回は、ロジックへの埋め込みに向けたMRAMのメモリセルと製造プロセスについて解説する。

単体MRAMと埋め込みMRAMのセル構造の違い

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。2017年12月に開催されたIEDMでは、「Memories for the future: device, technologies, and architecture(将来に向けたメモリデバイスの技術とアーキテクチャ)」と題したショートコースが開催された。このショートコースでは6本の技術講座が午前から午後にかけて実施された。

その中から、埋め込みメモリ技術(CMOSロジックとメモリを同じシリコンダイに混載する技術)に関する講座「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」が興味深かったので、その概要をシリーズでお届けしている。講演者はシリコンファウンダリー(半導体製造請け負いサービス企業)大手のGLOBALFOUNDRIESでeNVMフェローをつとめるDanny P. Shum氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、MRAMのメモリセルの構造と、データの読み出しと書き込みの原理を解説した。今回は、ロジックへの埋め込みに向けたMRAMのメモリセルと製造プロセスをご説明する。

前回で解説したように、MRAMのメモリセルは通常、1個のセル選択用トランジスタ(MOSFET)と1個の記憶素子「磁気トンネル接合(MTJ:Magnetic Tunneling Junction)」で構成される。ただし単体(スタンドアロン)のMRAMと、ロジック半導体への埋め込みを前提としたMRAMでは、セル構造が少し違う。具体的には、磁気トンネル接合の配置が異なる。

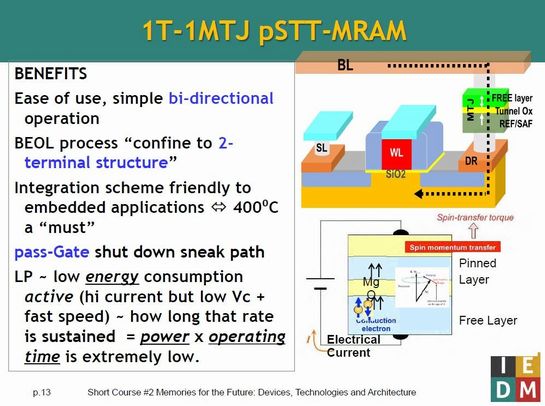

埋め込みMRAMのメモリセル構造。1個のセル選択トランジスタ(パスゲート)と1個の記憶素子(磁気トンネル接合(MTJ))でメモリセルを構成する。この図では分かりにくいが、埋め込みMRAMでは多層配線工程(BEOL: Back End Of Line)の途中で磁気トンネル接合(MTJ)を形成する。このため、MTJを形成するプロセスの温度が400℃以下という制限が加わる。出典:GLOBALFOUNDRIES(クリックで拡大)

埋め込みMRAMのメモリセル構造。1個のセル選択トランジスタ(パスゲート)と1個の記憶素子(磁気トンネル接合(MTJ))でメモリセルを構成する。この図では分かりにくいが、埋め込みMRAMでは多層配線工程(BEOL: Back End Of Line)の途中で磁気トンネル接合(MTJ)を形成する。このため、MTJを形成するプロセスの温度が400℃以下という制限が加わる。出典:GLOBALFOUNDRIES(クリックで拡大)単体のMRAMでは、記憶密度の向上を優先するので、セル選択用MOSFETのドレインあるいはソースのコンタクトに直接、あるいは近接して磁気トンネル接合をレイアウトする。製造工程としては、トランジスタとコンタクトを形成した直後に、磁気トンネル接合を形成する。それから多層配線の工程に入る。

これに対して埋め込み用MRAMでは、CMOSロジック半導体の製造工程をなるべく変更しないことを優先する。このため、セル選択用MOSFETを形成し、コンタクトと多層配線の一部を形成してから、磁気トンネル接合を形成する。GLOBALFOUNDRIESが提供する埋め込み用MRAMマクロの場合は、第5層金属配線(M5)と第6層金属配線(M6)の間に、磁気トンネル接合(MTJ)を形成する工程が入る。

配線工程の途中でMTJを形成するということは、プロセス温度に制約が加わることを意味する。具体的には400℃以下の温度で熱処理をしなければならない。プロセスの温度が低くなると、MTJの品質を上げにくくなる。この点では単体のMRAMとは違った難しさがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」