1つのシリコンを使い尽くす ―― 米国半導体メーカーの合理的な工夫:この10年で起こったこと、次の10年で起こること(27)(1/3 ページ)

半導体チップ開発は、プロセスの微細化に伴い、より大きな費用が掛かるようになっている。だからこそ、費用を投じて作ったチップをより有効活用することが重要になってきている。そうした中で、米国の半導体メーカーは過去から1つのチップを使い尽くすための工夫を施している。今回はそうした“1つのシリコンを使い尽くす”ための工夫を紹介していく。

シリコンチップを作るのには、膨大な費用がかかる。最新のチップでは百億円以上の開発費用をかけるものがほとんどだ。14/16nm世代、10/12nm世代、そして次世代の7nm世代では数十億円から数百億円が必要とされる。微細化すると製造コストはウナギ上りである。

筆者が代表を務めるテカナリエでは、チップ調査としてシリコンダイ面積を算出し1枚のウエハーからの取得数を求めて、欠陥密度などを加味してチップの単価を求めている。さらに、パッケージ構造や回路規模などによるテスト時間の推定や、設計にどのくらいの人員や期間が必要かなど、半導体の開発経験(テカナリエは複数のチップ開発に関与している)に基づいた比較的精度の高いコスト算出を行って、有償で情報提供を行っている。

そうした点からテカナリエでは新しいチップを調査目的で購入すると、ほとんどの場合、外観調査(パッケージ:素材、構造)を行ってからすぐにチップ開封を行う。シリコンダイのサイズや厚さ、採用されるプロセステクノロジーの判別、チップ上の文字図形情報の確認などを実施する。その後、配線層を剥離して配線の下に形成されるトランジスタ部を可視化してチップ内部の回路の読み取りを行っている。

最新のチップは多層配線を使っており、多いものでは15層を超える。通常でも10層程度のものが多い。10層程度の配線層は、X方向(横方向)に使われる5層と、Y方向(縦方向)に使われる5層に分かれ、これらの配線層が交互に形成され、億本単位の配線が成される。こうした多くの配線を剥離しない限り、チップ底部に存在するトランジスタ回路を見ることは100%できない。配線を薬品で剥離すれば回路が可視化でき、CPUやGPUの位置、形状、サイズ、コア数が明らかになる。さらにSRAMのサイズ(ビット数や階層構造)、USB、HDMIやPCI Express、MIPI、DDRなどのインターフェースの搭載も明らかになるわけだ。上記の調査には、どこのIPを導入してチップが作られているかも、判別してレポートする場合もある。

TIの通信チップにみる工夫

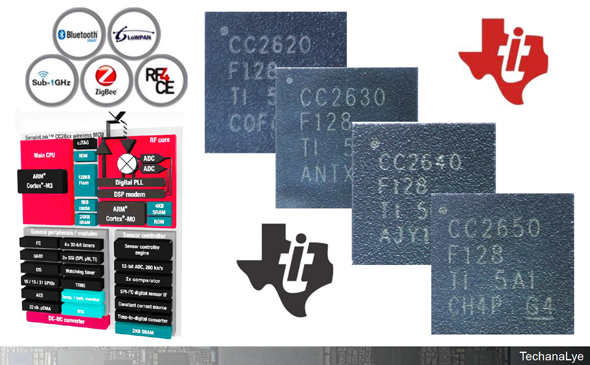

図1は、米Texas Instruments(以下、TI)が販売するIoT(モノのインターネット)端末向けのエッジ通信マイコン「CC26XX」の様子である。TIは、通信マイコン(RF回路とコントローラを1チップ化)では非常に多くの実績を持っている。13年も前のことだが、TIは通信用チップメーカーだったノルウェーのChipconを買収した。現在の半導体業界のM&Aは、会社の規模の拡大、製品ポートフォリオの拡大といった目的を実現する手段として活況を呈しているが、同じくして2000年代半ばにも多くのM&Aがなされていた。現在のトップ半導体メーカーの多くは2000年半ばにM&Aを繰り返した結果という見方もできるほどである(詳細は次回以降)

ChipconはZigBeeやBluetooth用の通信チップで多くの実績を残し、CC1000シリーズなどは現在でもさまざまな製品の分解で登場するほど売れている製品だ。1GHz以下の周波数帯を使用する「サブギガ通信」の品ぞろえも豊富で、TIが通信分野で躍進する原動力になっている。「8051」をCPUコアにした通信コントローラCC24XXは今なお、多くのIoTエッジ製品に最も使われているチップの一つである。買収した会社のブランドの継続を重視し、通信マイコンの型番にはChipconのイニシャル「CC」を使っていることでも、継続姿勢がうかがえる。その最新チップ製品群がCC26XXになる。

CC226XXはZigBee、Bluetooth、サブギガ、6LoWPANなど複数の通信方式に対応し、Armコアを2基(Cortex-M4コアと同M0コア)搭載し、フラッシュメモリを内蔵する通信マイコンとして販売されている。対応する通信方式を全て1つのチップで実現するのではなく、通信方式を組み合わせることで、CC2620〜CC2650までの4つのチップで提供される。ユーザーは使用したい通信方式に対応したチップを買えばよいわけだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か