ベールを脱いだ「ポスト京」CPU、アーキと性能を見る:倍精度ピーク性能は2.7TFLOPS以上(1/2 ページ)

富士通は2018年8月22日、ポスト「京」に搭載するCPUの詳細を公開した。同社は、LSIに関するシンポジウム「Hot Chips 30」(2018年8月19日〜21日、米国カリフォルニア州シリコンバレー)で、同チップに関する講演を行っている。本稿では、公開された講演資料から読み取れるアーキテクチャや性能を紹介する。

富士通は2018年8月22日、2021年頃の共用開始を目指すスーパーコンピュータ(スパコン)「ポスト『京』」に搭載するCPUの詳細を公開した。

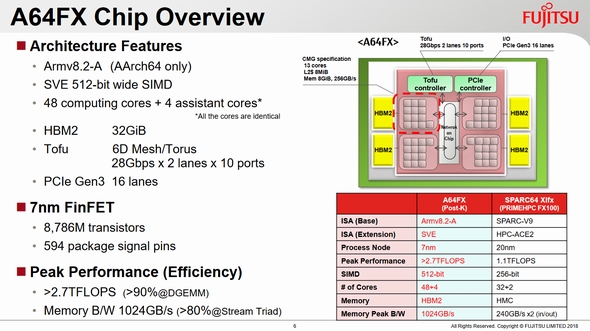

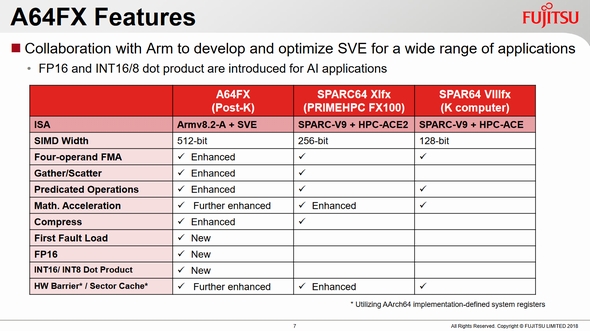

「A64FX」と命名されたこのCPUは、FP64(64ビット浮動小数点)におけるピーク演算性能で2.7TFLOPS以上を達成。FP32やFP16などによる演算も高いスループットを得られるとし、「従来のスーパーコンピュータが得意とするコンピュータシミュレーションだけでなく、ビッグデータやAI(人工知能)など、幅広い分野に適応するCPU」(同社)であるとする。

同社は、LSIに関するシンポジウム「Hot Chips 30」(2018年8月19日〜21日、米国カリフォルニア州クパチーノ)で、A64FXの技術概要を講演した。本稿では、公開された講演資料から読み取れるA64FXのアーキテクチャや性能を紹介する。

7nm FinFETを採用したA64FX、トランジスタ数は87億を超える

A64FXはベースISA(命令セットアーキテクチャ)にArmv8.2-A、SIMD拡張命令セットにSVE(Scalable Vector Extensions)を採用した「世界初」(富士通)のCPUとなる。7nm FinFETで開発され、48個の計算コアと4個のアシスタントコアを含むプロセッサ、合計32GバイトのHBM2メモリ、Tofuインターコネクトのコントローラー、PCI Express 3.0(PCIe Gen3)のコントローラーを集積する。

これによりトランジスタ数は87億8600万個に到達しており、「京」のCPUであるSPARC64 VIIIfxのトランジスタ数(約7億6000万個)から11倍超もの回路規模となる。生産を担当するファウンドリーは「非開示」(同社広報)としている。

HBM2と「高いメモリバンド幅性能を引き出すハードウェア技術」(同社)を実装したことによりにより、ピークメモリバンド幅は1024Gバイト/秒を実現し、メモリアクセスのベンチマークであるSTREAM Triadの実行効率は80%以上となった。CPU間を接続する6次元メッシュトーラスのTofuインターコネクトは、28Gビット/秒(bps)の2レーン構成で10ポートが用意されている。

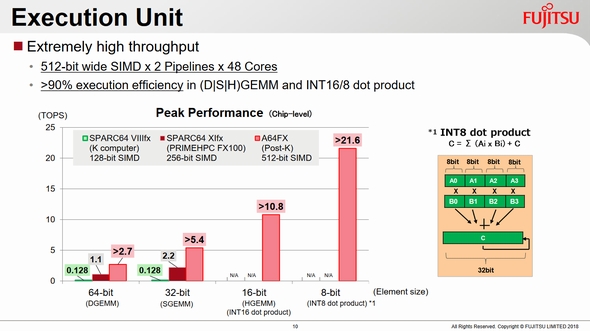

これらの足回りに下支えられ、行列積の実行効率はそれぞれの演算精度において90%以上と高い数値を示す。また、FP32演算(SGEMM)のピーク性能は5.4TOPS以上、INT8(8ビット整数)ドット積演算のピーク性能は21.6TOPS以上と、FP64演算(DGEMM)ピーク性能から線形的に増加している。

SPARC64の優れた長所を引き継ぎ、SIMDを強化したマイクロアーキテクチャ

ISAにArmを採用するA64FXだが、マイクロアーキテクチャにはSPARC64のスーパースカラー、アウトオブオーダー実行、分岐予測といった長所を引き継いだ。一方で、SPARC64ファミリーからの大きな改良点として、SVEの採用によるSIMDとプレディケートオペレーションの強化を挙げている。

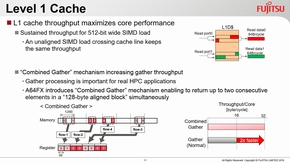

1つのコアに配置される演算実行部は、512ビット幅のSIMD FMA(浮動小数点積和演算)ユニットが2個、プレディケートユニットが1個、整数ユニットが4個(このうち2個がアドレス生成ユニットと共有)で構成されるとみられる。SPARC64 VIIIfxではSIMD幅が128ビットとなっていた。また、同じく512ビット幅のSIMDロードを2つ、または512ビット幅のSIMDストアを1つ実行できるメモリアクセス部を持つ。

その他にデコード部、汎用レジスタやプレディケートレジスタ、浮動小数点数レジスタといったレジスタリード部、L1データキャッシュ、L2キャッシュの強化が図られている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

「A64FX」のパッケージ写真 出典:富士通

「A64FX」のパッケージ写真 出典:富士通