ベールを脱いだ「ポスト京」CPU、アーキと性能を見る:倍精度ピーク性能は2.7TFLOPS以上(2/2 ページ)

コアとL2キャッシュ、メモリコントローラーをまとめるCMG

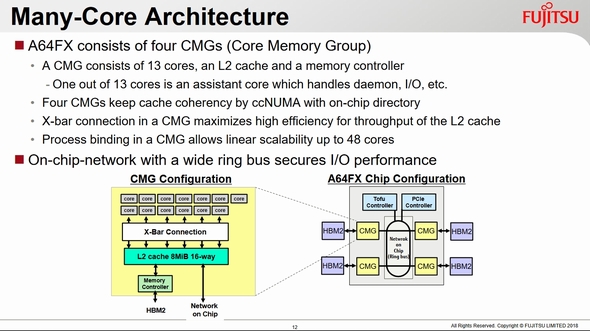

A64FXは、13個のコアと8MバイトのL2キャッシュ、メモリコントローラーを1つのグループとした「Core Memory Group(CMG)」という要素が4個集まることで構成される。HBM2は、1個のCMGに8Gバイトがぶら下がるように接続され、各CMGはチップ内ネットワークのリングバスによるccNUMA(cache-coherent NUMA)でキャッシュコヒーレンシが保たれている。

CMG内にある13個のコアの内、1個がOSやI/O処理用のアシスタントコアとして割り当てられ、計算に用いられるコア数は48個となる。それぞれのコアはクロスバー接続されており、L2キャッシュへのスループット高効率化を果たした。また、CMG内でプロセスのバインディングを行うことで、48個の計算コアを用いた場合でも線形的なスケーラビリティを得ることができるとしている。

既報(ポスト京は高密度がカギ、富士通が試作チップを公開)では、「CPUパッケージは2種類の仕様があり、1つ目の仕様『計算ノード』は、48個の計算コアとOSやI/Oを処理する用途で2個のアシスタントコアで構成。もう1つの仕様『IO&計算ノード』では、48個の計算コアと4アシスタントコアを装備する」とお伝えしていた。

しかし、「計算ノード」と「IO&計算ノード」で2種類のチップを用意するわけではなく両方ともA64FXを用いるようで、アシスタントコアの個数は、「ソフトウェアによる制御で有効、無効化を行う」(同社広報)とした。

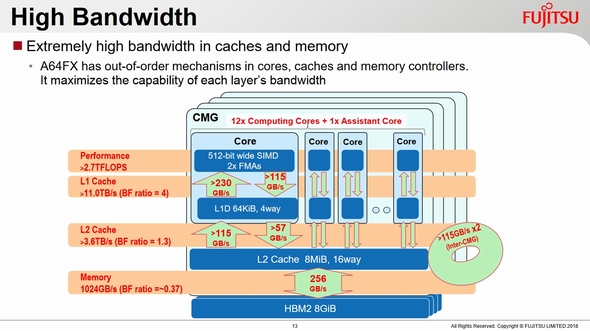

また、メモリからコアまでのピークバンド幅も公開。アウトオブオーダー機構をコア、キャッシュ、メモリコントローラーに組み込んだことによる広帯域性能をアピールする。

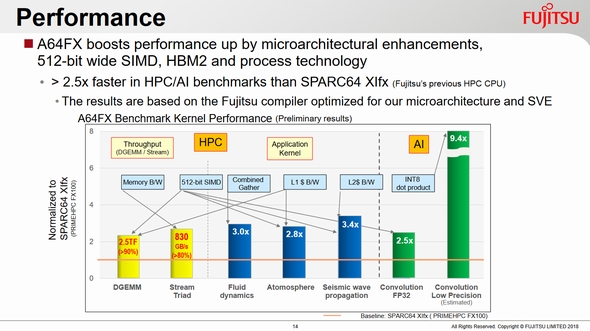

前世代CPUから約3倍以上の実行性能向上を達成、AIでは9倍以上も

これらの強化により、アプリケーション実行性能において前世代CPUから大きな性能向上を果たしたとする。富士通はSPARC64 XIfxを基準とした各アプリケーションの性能速報値を発表しており、HPC(High Performance Computing)用途例として、流体解析では3倍、大気モデルでは2.8倍、地震波伝搬では3.4倍の性能を発揮するとしている。

また、AI用途での性能向上例も示しており、FP32による畳み込み層計算では2.5倍、低精度(INT8)を用いた畳み込み層計算では9.4倍(予測値)の改善があった。

その他、講演ではA64FXのパワーマネジメントやRAS(Reliability, Availability, Serviceability)機能、ポスト京のソフトウェア開発体制を紹介した。講演資料のサマリーでは、富士通がArmアーキテクチャのプロセッサ開発を継続する方針であることを明記しており、同社の意気込みを感じさせた。

関連記事

「ポスト京」の試作CPUが完成、機能試験を開始

「ポスト京」の試作CPUが完成、機能試験を開始

富士通と理化学研究所は2018年6月21日、ポスト「京」スーパーコンピュータ(スパコン)に搭載するCPUの試作チップが完成し、機能試験を開始したと発表した。 ポスト京は高密度がカギ、富士通が試作チップを公開

ポスト京は高密度がカギ、富士通が試作チップを公開

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ポスト「京」スーパーコンピュータ(スパコン)に搭載される予定の「CPUパッケージ」とCPUパッケージを搭載した「CPUメモリユニット」の試作機を公開した。 ARMの新ベクトル命令「SVE」、ポスト京に採用へ

ARMの新ベクトル命令「SVE」、ポスト京に採用へ

米国で開催された「Hot Chips 28」において、ARMが新しいベクトル命令「SVE(Scalable Vector Extensions)」を発表した。富士通が、2020年を目標に開発しているポスト「京」スーパーコンピュータに採用されることが決まっている。 UMCが三重富士通を買収へ、全株式の取得で合意

UMCが三重富士通を買収へ、全株式の取得で合意

台湾の専業ファウンドリーであるUMC(United Microelectronics Corporation)と富士通セミコンダクターは2018年6月29日、三重富士通セミコンダクター(MIFS)の全株式をUMCが取得することで合意したと発表した。 富士通三重工場の売却も決定……これからどうなる? 日本の半導体工場

富士通三重工場の売却も決定……これからどうなる? 日本の半導体工場

2018年6月末、旧富士通三重工場を運営する三重富士通セミコンダクターが台湾のUMCに売却され、2019年1月にはUMCの完全子会社となると発表された。今回の売却も含めて“日本の半導体工場”の現状および、今後の方向性について考えてみたい。 富士通のAIプロセッサ、演算精度とμアーキに工夫

富士通のAIプロセッサ、演算精度とμアーキに工夫

富士通は、同社のプライベートイベント「富士通フォーラム2018 東京」(2018年5月17〜18日、東京国際フォーラム)で、ディープラーニング処理に特化したプロセッサ「DLU(Deep Learning Unit)」を展示した。競合となる既存のアクセラレーターと比較して、10倍の電力性能比を実現するとしている。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長