2D NANDフラッシュの限界と3D NANDフラッシュへの移行:福田昭のストレージ通信(114) 3D NANDのスケーリング(2)(1/2 ページ)

今回は、2D NANDフラッシュメモリの記憶容量が拡大していった経緯と、2D NANDフラッシュ技術から3D NANDフラッシュ技術への転換について解説する。

2D NANDフラッシュの記憶容量拡大とその限界

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要を今回からシリーズでお届けする。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、講演のアウトラインと、NANDフラッシュメモリの需要が拡大していく理由をご説明した。今回は、既存技術である2D NANDフラッシュメモリの記憶容量が拡大していった様相を振り返るとともに、2D NANDフラッシュ技術から3D NANDフラッシュ技術への転換を解説しよう。

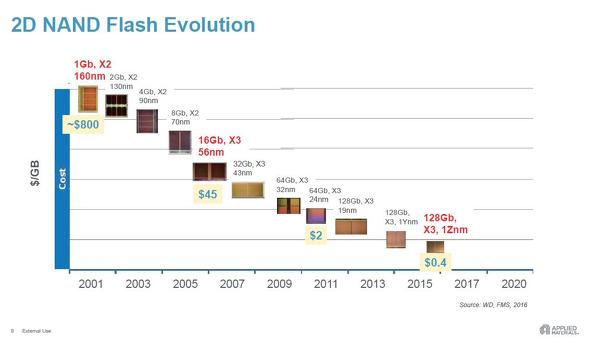

既存技術である2D NANDフラッシュメモリの記憶容量(シリコンダイ当たり)は、西暦2000年ころには1Gビットに達した。このころの記憶容量当たりのコスト(以下は「Gバイト当たりのコスト」で表記)はおよそ800米ドルである。その後、2D NANDフラッシュは微細化を中心とする技術開発によって順調に記憶容量と記憶密度を伸ばしてきた。2006年ころには記憶容量が16Gビットと16倍に拡大し、Gバイト当たりのコストは45米ドルと約18分の1に減少する。2011年には記憶容量が64Gビットとさらに4倍に増え、Gバイト当たりのコストは2米ドルとさらに20分の1以下に下がった。

しかし2011年ころから、2D NANDフラッシュメモリの微細化が困難になってくる。主な理由は3つ。1つは、セルに蓄積可能な電荷量が極めて少なくなってきたこと。もう1つは、隣接するメモリセル間の電気的な干渉が増大し、データ読み書きの長期信頼性を損ない始めたこと。最後は、リソグラフィ技術に限界が見え始めたことである。

懸命の努力もむなしく、2013年〜2015年には2D NANDフラッシュメモリの微細化と大容量化は限界に達する。シリコンダイ当たりの記憶容量は128Gビットに増大し、Gバイト当たりのコストは0.4米ドルまで下がった。2015年を区切りと考えると、15年間で記憶容量は128倍に増加し、コストは2000分の1に低下したことになる。恐ろしいほど高い、開発ペースであることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 全固体電池の製造プロセス簡素化、東北大が新手法

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める