2D NANDフラッシュの限界と3D NANDフラッシュへの移行:福田昭のストレージ通信(114) 3D NANDのスケーリング(2)(2/2 ページ)

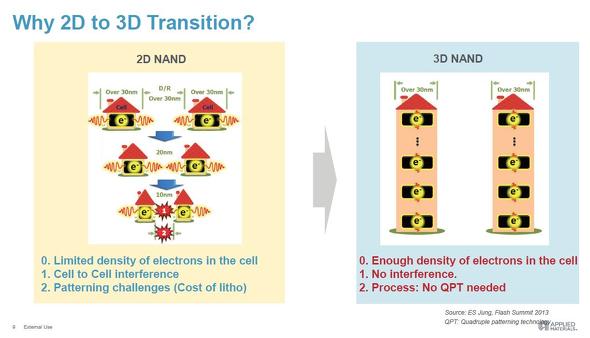

3D NANDによって2D NANDの課題を全て解決する

2D NANDフラッシュ技術の限界をクリアする技術として3D NANDフラッシュ技術が開発され始めたのは、2000年代の後半からだ。基本的な考え方は単純で、メモリセルを平面状(シリコン表面と平行な方向)につなげたストリング(メモリセルストリング)を、垂直に立てる(シリコン表面と垂直な方向に伸ばす)ことによってシリコン面積当たりの記憶容量を増やそうというものである。

垂直に伸ばしたストリングの間隔は、2D NANDフラッシュのメモリセルの間隔よりも広い。それでもストリングを構成するメモリセルの数(垂直方向の積層数)を十分に増やせば、2D NANDよりも記憶密度を上げられる。しかもメモリセルが蓄積可能な電荷量が増え、隣接するメモリセル間の電気的干渉は大幅に小さくなり、リソグラフィ技術が緩くなる。2D NAND技術が抱える課題の全てが、解決可能なのである。

微細化ではなく、高層化によって記憶密度を拡大

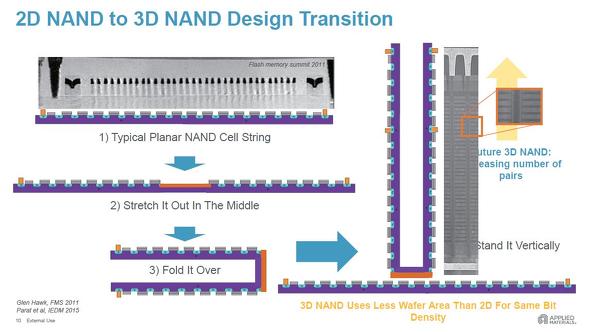

それでは、3D NANDフラッシュ技術のメモリセルストリングとはどのようなものか。Kang氏は2D (プレーナー)NANDフラッシュ技術のメモリセルストリングを3D NANDフラッシュ技術へと変換する手順を、一種のイメージとして説明していた。

プレーナーNANDフラッシュのメモリセルストリング(セルトランジスタの連なり)をまず、中央部分で伸ばしてから折りたたむ。すると半分のセルストリング同士が背中(チャンネル)を向けて並ぶようになる。

次に、この折りたたんだU字型のセルストリングを、垂直に立てる。このとき、セルストリングの中央部分がシリコン表面と接する。すると、プレーナーNANDのセルストリングに比べると、シリコン表面で占有する面積が、少なくなることが分かる。これが3D NANDフラッシュ技術におけるメモリセルストリングとなる。

3D NANDフラッシュ技術では、記憶密度の拡大手段は、高層化である。セルストリングを構成するメモリセルの積層数を増やすことによって、シリコン面積当たりのセル数、すなわち記憶するビット数を拡大する。リソグラフィ技術による微細化には、基本的には頼らない。

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

MRAMのメモリセルと読み書きの原理

MRAMのメモリセルと読み書きの原理

今回は、MRAMのメモリセルの構造と、データの読み出しと書き込みの原理をご説明する。 磁気トンネル接合(MTJ)におけるSRAM代替用とフラッシュ代替用の違い

磁気トンネル接合(MTJ)におけるSRAM代替用とフラッシュ代替用の違い

SRAM代替用MRAMとフラッシュメモリ代替用MRAMでは、磁気トンネル接合(MTJ)の特性がどのように異なるのだろうか。 記憶容量と書き換え回数から最適な埋め込みメモリを選択

記憶容量と書き換え回数から最適な埋め込みメモリを選択

半導体デバイス技術に関する国際会議「IEDM」で行われたセミナー「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」の概要を今回からシリーズで紹介する。 2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。 埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

埋め込みMRAMの磁気トンネル接合(MTJ)に要求される条件

多層配線の製造工程に磁気トンネル接合(MTJ)の製造プロセスを組み込むと、どのようなことがMTJに要求されるようになるのか。今回は、その要求を解説する。 Samsung、18年4〜6月期も半導体シェア首位を維持

Samsung、18年4〜6月期も半導体シェア首位を維持

Samsung Electronicsは、好調なメモリ市場の後押しを受け、2018年第2四半期の半導体サプライヤーランキングにおいてIntelを抑え首位を維持した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- 300mmファブ装置の投資額、2年連続で2桁成長へ

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- Intelがアイルランド工場を完全子会社化、Apolloから49%買い戻し

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」