“通常とは違う過程で登場”したGPU「Turing」は何が新しいのか:RTコア1個で性能はCPUの100倍(1/3 ページ)

NVIDIAが2018年8月に発表した新世代GPUは、それまでのPascalや最新のVoltaにはない「Ray Tracing」専用ハードウェアを実装した。その意味と効果とは。

「コア2割増しで性能3割増し」の理由とは

NVIDIAは、2018年8月に新世代のアーキテクチャ「Turing」を発表し、9月末にもこの世代のGPUを載せたグラフィックスカードが登場する。既に8月に開催したSIGGRAPHやGameconで海外では発表会を行っているが、9月13日から14日にかけて東京で開催した「GTC Japan 2018」において日本の関係者に向けてその概要を紹介した。この記事では、GTC Japanの14日に実施したテクニカルセッションに登壇したエヌビディアでQuadro プロダクトマネージャー シニアソリューションアーキテクトを務める柿澤修氏の講演内容から、Turingアーキテクチャの特長を解説する。

柿澤氏が講演冒頭で発した「通常とは違う経過で登場した」という言葉は、NVIDIAがこれまで開発してきた従来のGPUとTuringアーキテクチャの違いをとても端的に表現している。同様に、Turingアーキクチャを採用したGPUの名称に「Quadro RTX」のように、これまでの“G”TXではなく、“R”TXをつけるようになったのも、NVIDAがTuringアーキテクチャで重視する方向性を示している。

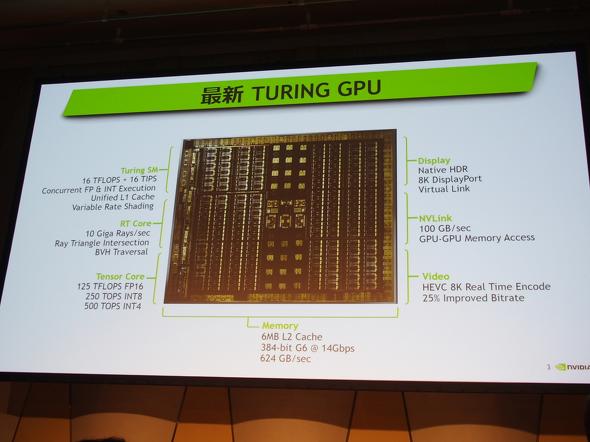

柿澤氏は、この「R」を「リアルタイムレイトレーシング(Real time Ray tracing)を意識した、これまでとは全く違うアーキテクチャ」を示すものと語る。Turingアーキテクチャでは、レイトレーシング処理に特化した「RTコア」、ディープラーニングに特化した「Tensorコア」が追加された他、ディスプレイ出力では8K DisplayPortをサポートし、ビデオエンコードではHEVC 8Kのリアルタイムエンコードに対応するようになった。また、マルチGPU環境(NVIDIAでいうところのSLI構成)を構築するNVLinkは2リンク接続に対応し、グラフィックスメモリではGDDR6をサポートした。テクニカルセッションで示したTuringアーキテクチャ採用GPUの演算処理能力は次のようになる。

| Turing SMユニット | 16TFLOPS+16TIPS(1秒あたりの整数演算実行能力) |

|---|---|

| RTコア | 10 Giga Rays/秒 |

| Tensorコア | 125TFLOPS(FP16)、250TOPS(INT8)、500TOPS(INT4) |

| NVLink | 100Gバイト/秒(GPU-GPU Memory Access) |

| Graphics Memory | メモリバス幅384ビット、転送レート14Gビット/秒、メモリ帯域624Gバイト/秒 |

Turingアーキテクチャを採用したGPUダイと実装した仕様に処理能力。なお、NVIDIAではGPUコンピューティングに特化した「Volta」アーキテクチャで既にTensorコアを実装している(クリックで拡大)

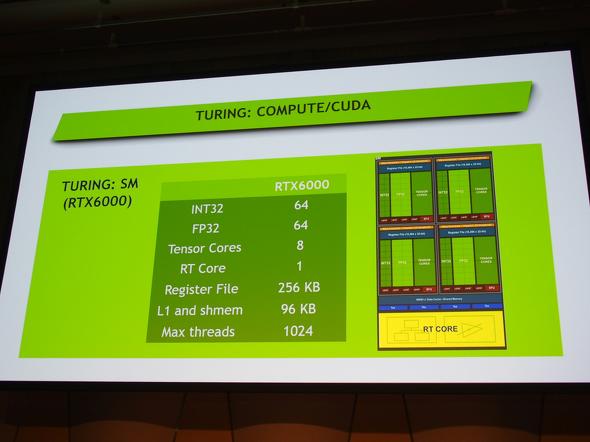

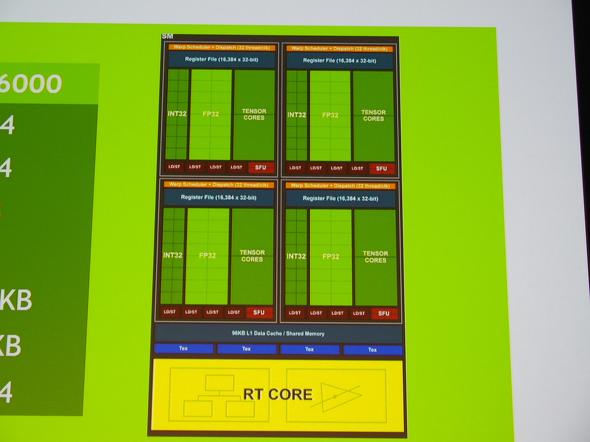

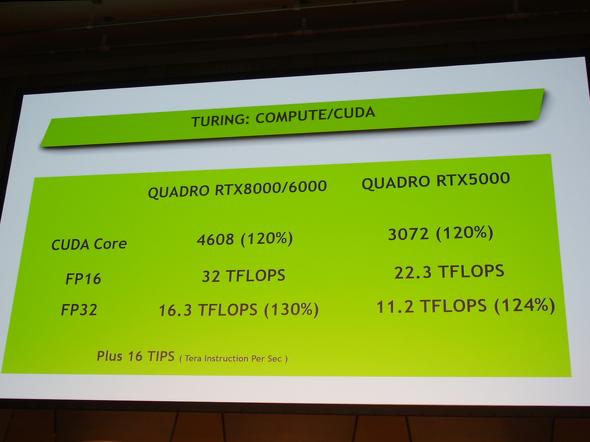

Turingアーキテクチャを採用したGPUダイと実装した仕様に処理能力。なお、NVIDIAではGPUコンピューティングに特化した「Volta」アーキテクチャで既にTensorコアを実装している(クリックで拡大)前世代のPascalを採用した「Quadro P6000」とTuring採用の「Quadro RTX6000」のCUDAコアの数を比較するとQuadro P6000の3840個に対してQuadro RTX6000は4608個と約2割増しとなる。しかし、柿澤氏は「CUDAコアは2割増しなのに処理能力は3割増し。この理由がTuringの説明でメインになる」と述べるように、CUDAコアをまとめて構成する演算ユニット「SM」(Streaming Multiprocessor)の機能と構成が大きく変化している。なお、Quadro RTX6000では72個のSMを実装する。

Turingアーキテクチャで実装する各種演算ユニットの数とPascal世代同クラスGPUとの比較。なお、FP16はTuring世代で初めて実装している。下にある「Plus 16 TIPS」がTuringで可能となったFPとINTの同時実行による処理能力向上分をカウントしている(クリックで拡大)

Turingアーキテクチャで実装する各種演算ユニットの数とPascal世代同クラスGPUとの比較。なお、FP16はTuring世代で初めて実装している。下にある「Plus 16 TIPS」がTuringで可能となったFPとINTの同時実行による処理能力向上分をカウントしている(クリックで拡大)Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増