“通常とは違う過程で登場”したGPU「Turing」は何が新しいのか:RTコア1個で性能はCPUの100倍(2/3 ページ)

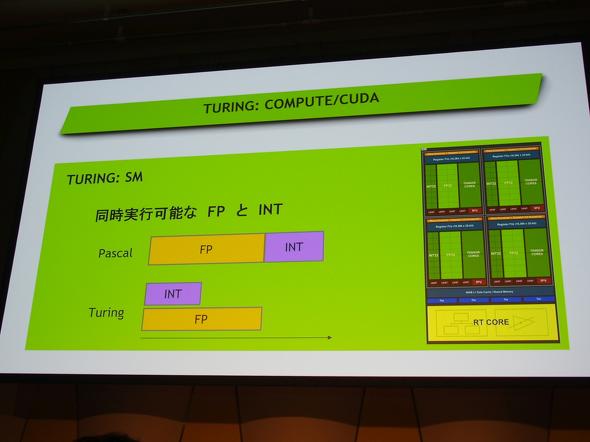

浮動小数点演算と整数演算の同時実行が可能に

演算機能の面では、Pascalまで浮動小数点演算と整数演算は命令のあった順に逐次処理していたが、Turingではこれらを同時に処理できるようにした。また、構成ではTensorコアとRTコアを加えただけでなく、L1(1次キャッシュメモリ)に対してバス幅をPascalアーキテクチャの2倍に、容量を2.7倍にした上でレイテンシを削減、また、L2(2次キャッシュメモリ)の容量も2倍に増やすことで演算処理速度の改善を試みている。柿澤氏は「これらの相乗効果で性能が30%向上した」と訴求する。

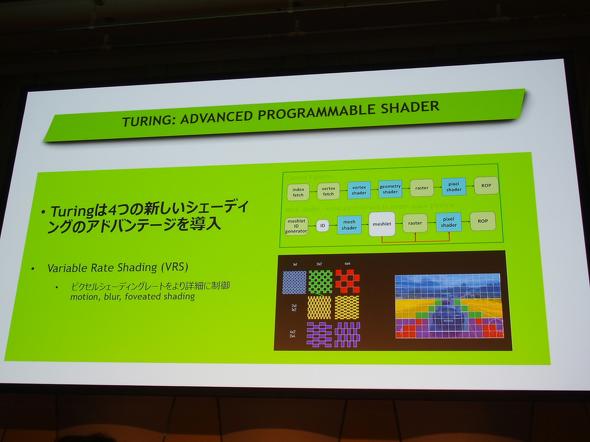

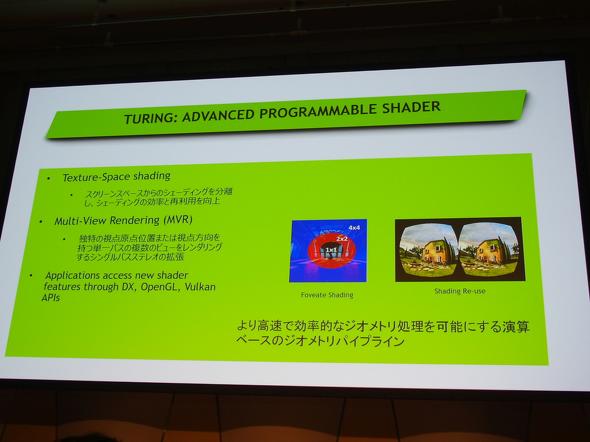

また、プログラマブルシェーダーでは新たに「Mesh Shading」に「Variable Rate Shading」(VRS)、「Texture-Space Sharing」、そして「Multi-View Rendering」(MVR)の機能を用意した。「これらのシェーディング機能の追加で、効率の良いプログラムが可能になる」と柿澤氏は説明する。また、後述するRTコアが処理するRay Tracingでこれらのシェーダー処理をパイプラインとして実施するため、その部分でも効率の高いプログラムが可能になるという。

| 新規に導入したシェーダ | 導入で期待できる主な効果 |

|---|---|

| Mesh Shading | より高速で効果的なジオメトリ処理を可能にする演算ベースのジオメトリパイプライン |

| Variable Rate Shading | motion、blur、foveatedなど別個に扱っていたシェーディングを一度に処理できるようになる |

| Texture-Space Sharing | スクリーンスペースからのシェーディングを分離し、シェーディングの効率と再利用を向上 |

| Multi-View Rendering | 従来、右用左用それぞれで描画していたVR処理で、両画面共通部分は一度だけ描画し、右と左だけで必要な部分だけをそれぞれ描画することで、描画処理を高速にする |

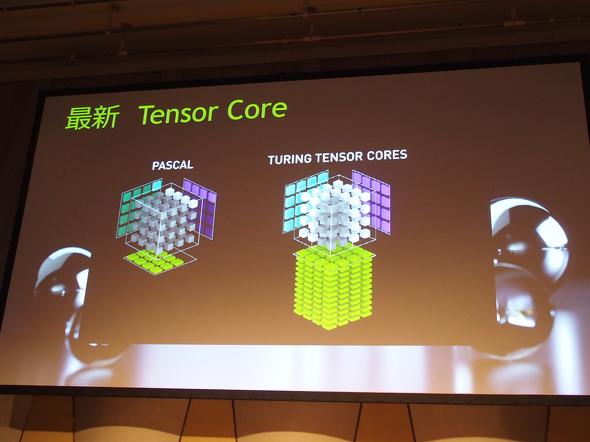

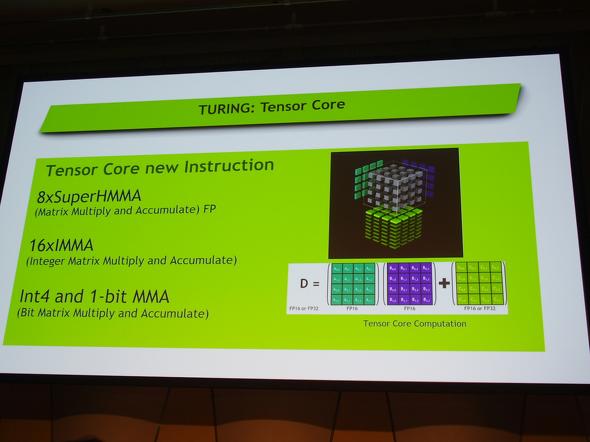

TuringのTensorコアはVoltaと何が異なる

ディープラーニングに特化したTensorコアは、4×4の行列における積和演算を処理するハードウェアエンジンだ。その能力は1サイクルで128の演算を処理できる。Turingに実装したTensorコアには、FP16、INT8、INT4を組み込んでおり、それぞれの演算処理能力は、FP16で130.5TFLOPS、INT8で261TOPS、INT4で522TOPSに達する。TuringのTensorコアで実装したINT8とINT4は、VoltaのTensorコアでサポートしていない。Volta自体はINT8命令を実行できたが、これはSMで演算しており、このTensorコアの変更によってTuring実装TensorコアのINT8演算処理能力はVoltaの4倍になったと柿澤氏は説明する(FP16はVoltaと同等)。また、Tensorコアで扱える命令セットも増えている。加わったのは「8xSuperHMMA」(Matrix Multiply and Accumulate)と「16xIMMA」(Integer Matrix Multiply and Accumulate)、そして、「Int4 and 1-bit MMA」(Bit Matrix Multiply and Accumulate)だ。

柿澤氏は、GPUコンピューティング(そしてその目的がディープラーニング利用)を重視するVoltaとは性格が異なる、グラフィックス処理を重視するTuringにディープラーニングに特化したTensorコアを実装する、ひいてはFP16を実装する理由として、AIを利用するアンチエイリアシング技術「DLSS」(Deep Learning Super Sampling)を挙げる。DLSSは、ディープラーニングで得た学習成果を描画処理における補完(低解像度のデータからより高解像度の描画処理を行う場合、データの足りないピクセルの描画データを推測して補完して求める)に用いることで、線のがたつき(ジャギー)や色階調の増加、高解像度描画を可能にする。従来は、データが足りないピクセルの描画データに対して周囲の情報から「数学」的に求めていたが、DLSSでは、それまでに処理してきた描画処理の結果から適切なデータを推測して求めることでより高品位なグラフィックスを実現するとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増