3D NANDフラッシュメモリの断面構造と製造工程:福田昭のストレージ通信(116) 3D NANDのスケーリング(4)(1/2 ページ)

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。

3D NANDフラッシュメモリの断面構造

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、2D NANDフラッシュ技術と3D NANDフラッシュ技術におけるメモリセルアレイ構造の違いを鳥瞰(ちょうかん)図を用いて説明した。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。

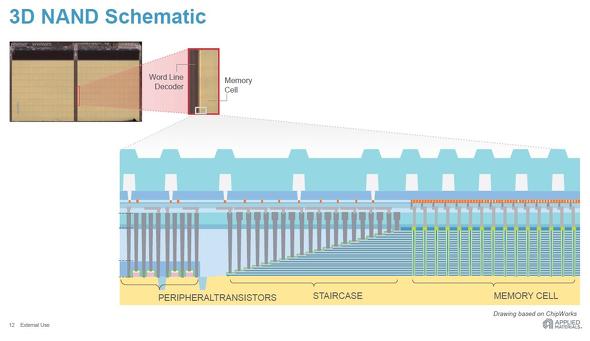

3D NANDフラッシュメモリの断面構造。左上はシリコンダイ写真。右下は、ワード線デコード回路とメモリセルアレイの境界付近を切り出した断面の構造図。構造図の左端は周辺回路。中央は制御ゲート(ワード線)の引き出し(ステアケース)。右端はメモリセルアレイ (クリックで拡大) 出典:Applied Materials

3D NANDフラッシュメモリの断面構造。左上はシリコンダイ写真。右下は、ワード線デコード回路とメモリセルアレイの境界付近を切り出した断面の構造図。構造図の左端は周辺回路。中央は制御ゲート(ワード線)の引き出し(ステアケース)。右端はメモリセルアレイ (クリックで拡大) 出典:Applied Materials3D NANDフラッシュメモリの断面構造は、マイクロプロセッサやSoC(system on a chip)などの一般的なロジック半導体の断面構造とも、DRAMやNORフラッシュメモリなどの半導体メモリの断面構造とも、大きく違う。最大の違いは、膨大な数で林立する細長い柱状の構造物の存在である。

一般的な半導体デバイスの断面構造は、最下層にMOSトランジスタがあり、その上にCMOS回路を形成するための相互接続があり、その上に金属の多層配線層がある。配線層間を接続する柱やトランジスタと配線層をつなぐ柱は存在しているものの、それほど長くはない。

ところが3D NANDフラッシュメモリでは、半導体シリコンの全体に渡って長い柱がびっしりと並んでいる。極細で長い柱は、主に3種類ある。1つは、メモリセルストリングを形成するための柱(チャネルホール、メモリホールなどと呼ばれている)である。もう1つは、メモリセルの制御ゲート(ワード線)層と金属配線層を結ぶための柱である。最後は、周辺回路のMOSトランジスタと金属配線層を結ぶための柱である。

なぜこのような細長い柱が林立するのか。3D NANDフラッシュでは、メモリセルストリングの上に金属配線層が形成されているからだ。例えば48層、64層といったセルの積層数を考えよう。この積層数は、高性能ロジックの金属配線層数をはるかに超える。異常な層数である。層数の多さは、構造の高さに直結する。しかもロジックの金属配線では最下層の配線と最上層の配線を直結するようなレイアウトはほぼあり得ない。せいぜい、隣接する偶数層あるいは奇数層をつなぐくらいだ。

ところが3D NANDフラッシュでは、48層や64層といった高さのその上に金属配線層が存在し、中間がない。シリコン表面、すなわち最下層に設けたMOSトランジスタの周辺回路は、細長い柱を通して48層や64層よりもさらに上の層へと、接続されることになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増