NVIDIAが語るVoltaとTuring、最新GPUはこう使おう:GTC Japan 2018(1/4 ページ)

NVIDIAのGPUアーキテクチャである「Turing」と「Volta」。これら2つのアーキテクチャでは、RTコアとTensorコアという2つのユニットが性能躍進の立役者となった。GTC Japan 2018の講演から、アーキテクチャをおさらいし、最新GPUを効率的に活用するための手法を紹介する。

NVIDIAは2018年8月、新世代GPUアーキテクチャ「Turing」を発表した。世界初のハードウェアによるリアルタイムレイトレーシングをうたうTuring。その実現には、「RTコア」の実装が大きく寄与しているとされる。そんな立役者のRTコアだが、何をやっているものなのか、そしてグラフィックス以外のHPC(High Performance Computing)やAI(人工知能)用途でRTコアは使えるのか、といった点が気になるところだ。

また、Turingの前世代となる「Volta」からアーキテクチャに変化が起こった。その代表的な点が「Tensorコア」の導入だ。これにより、Voltaは特にディープラーニング用途で大幅な性能改善を果たしており、Voltaを実装するHPC向けGPUボード「Tesla V100」は多くのスーパーコンピュータ(スパコン)に搭載されている(関連記事:産総研AIスパコン、TOP500世界5位に)。Tensorコアの活用で、ディープラーニングの演算処理はなぜ高速化することができたのだろうか。

本稿では、「GTC Japan 2018」(2018年9月13〜14日、グランドプリンスホテル新高輪 国際館パミール)で開催された講演「Turing/Volta Deep Dive: architecture and performance optimization」(講演者:エヌビディア シニアデベロッパーテクノロジーエンジニア 成瀬彰氏)の内容から、TuringとVoltaのアーキテクチャをおさらいし、講演で発表された最新GPUを効率的に活用するための手法も簡単に紹介する。

アーキテクチャの大部分を共有するVoltaとTuring

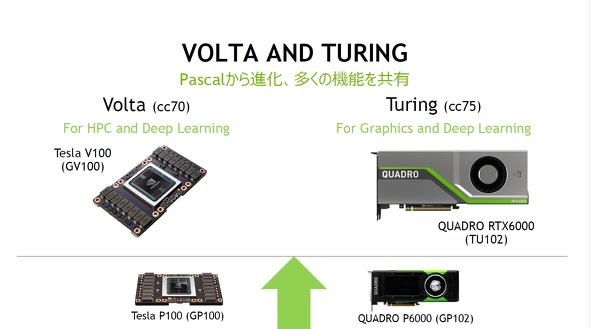

今回の講演では、VoltaとTuringの2つのアーキテクチャにフォーカスしている。成瀬氏は、この2つのアーキテクチャについて「狙っているアプリケーションは異なるが、(VoltaとTuringは)基本的なアーキテクチャのかなりの部分を共有している」と語る。

この点は、アーキテクチャ世代をCUDA上で識別する指標“Compute Capability”にも表れており、「VoltaのCompute Capabilityは7.0、それに対してTuringは7.5。われわれは全く違うアーキテクチャを開発したとき、(Compute Capabilityの)最初の位の数字を変える。これが全てを物語っている」(成瀬氏)とする。実際に、Pascal世代ではCompute Capabilityの最初の位の数字が“6”となる。

では、VoltaとTuringが主戦場とするアプリケーションはどこになるのか。その問いに対して成瀬氏は、VoltaはHPCとディープラーニング、そしてTuringはグラフィックスとディープラーニングであると明言する。そのため、Turingではレイトレーシングに特化したユニットであるRTコアを実装したことがハイライトとして挙げられるが、成瀬氏は「(TuringはVoltaから)決してブランチしたわけではない。アーキテクチャの重要な基礎は共有していて、付加的な部分で異なる」と重ねて強調した。

VoltaとTuringのアプリケーション。Pascal世代であるTesla P100の後継はVolta世代のTesla V100、Quadro P6000の後継がTuring世代のQuadro RTX6000と紹介されている(クリックで拡大) 出典:NVIDIA

VoltaとTuringのアプリケーション。Pascal世代であるTesla P100の後継はVolta世代のTesla V100、Quadro P6000の後継がTuring世代のQuadro RTX6000と紹介されている(クリックで拡大) 出典:NVIDIAVoltaとTuringのアーキテクチャをおさらい

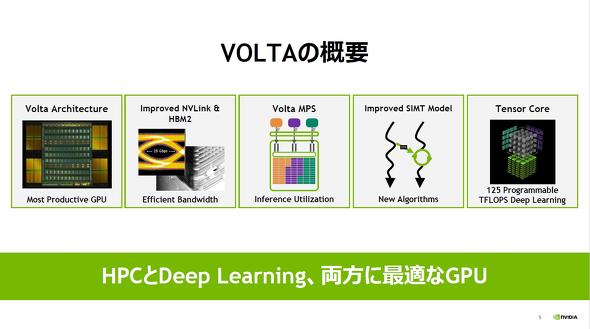

まず、Voltaのアーキテクチャや新機能について振り返る。Voltaでは、前述のTensorコア採用がトピックとして挙げられるが、その他にもバンド幅900Gバイト/秒のHBM(High Bandwidth Memory)2とバンド幅300Gバイト/秒の第2世代NVLinkの採用による足回りの強化、複数のプログラムで演算リソースをシェアできるVolta MPS(Multi-Process Service)、「Independent Thread Scheduling」によるSIMT(Single Instruction, Multiple Thread)の拡張がある。

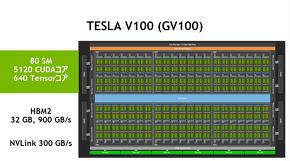

Voltaアーキテクチャを採用したチップであるGV100(Tesla V100)は、80個のSM(Streaming Multiprocessor)が搭載され、チップ全体では5120個のCUDAコア、640個のTensorコアを集積した。同チップの総トランジスタ数は211億個。NVIDIAの特注12nmプロセスである12FFNで製造されるが、公称ダイサイズは815mm2と非常に大きい。多くの露光装置では最大露光面積が26.0×33.0mmとなっており、GV100のダイサイズはこの数値に非常に近い。GV100は最大サイズのGPUであるとして各所で報じられている。

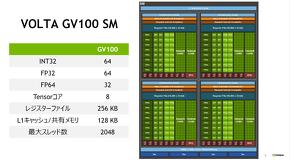

1個のSMにある演算ユニットは、INT32(32ビット整数)が64個、FP32(32ビット浮動小数点)が64個、FP64が32個、Tensorコアが8個。レジスターファイルは256Kバイトと前世代から変わりないが、L1キャッシュとシェアード(共有)メモリが「共有型に先祖帰り」(成瀬氏)しており、合計128Kバイトとなった。最大スレッド数は2048だ。

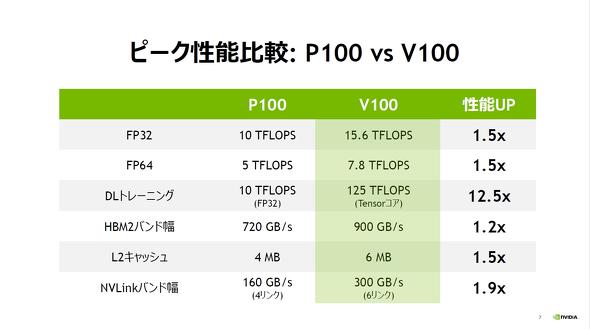

GV100を搭載するTesla V100のピーク性能は、FP32では15.6TFLOPS、FP64では7.8TFLOPSと、Pascal世代のTesla P100と比較して1.5倍の性能向上を果たした。特にFP64の性能向上について、成瀬氏は「ディープラーニングに向けてのみGPUを進化させているのではなく、今までCUDAを育ててきてくれたHPCコミュニティーへの機能拡張も続けている」証だとしている。また、ディープラーニングの学習時には後述するTensorコアを活用することで125TFLOPSのピーク性能を発揮。この数値は、Tesla P100でFP32による学習を行う場合から12倍超の性能向上となる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

成瀬彰氏

成瀬彰氏