高アスペクト比の細長い孔をハードマスクによって形成(続き):福田昭のストレージ通信(122) 3D NANDのスケーリング(10)(1/2 ページ)

前回に続き、3D NANDフラッシュ製造におけるキープロセスの1つ、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」を取り上げる。今回は、同技術の異方性エッチングについて解説する。

ハードマスクと異方性エッチングを組み合わせる

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュ製造における重要技術(キープロセス)の1つである「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」技術の前半部分に相当する、ハードマスクについて説明した。今回は同じ技術の後半部分に相当する、異方性エッチングについて解説する。

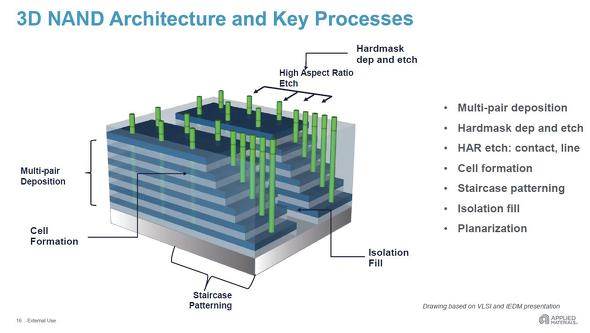

3D NANDフラッシュメモリの立体構造(左)と、製造における重要技術(キープロセス)(右)。左の立体構造図で、緑色の細長い円柱が高アスペクト比パターン形成技術を必要とする。マルチペア薄膜を貫通するスルーホールと、ステアケースと上部を接続するコンタクトである。このほか、ステアケース中央にある細長い溝(スリット)も、高アスペクト比のパターン形成技術が必要となる。出典:Applied Materials(クリックで拡大)

3D NANDフラッシュメモリの立体構造(左)と、製造における重要技術(キープロセス)(右)。左の立体構造図で、緑色の細長い円柱が高アスペクト比パターン形成技術を必要とする。マルチペア薄膜を貫通するスルーホールと、ステアケースと上部を接続するコンタクトである。このほか、ステアケース中央にある細長い溝(スリット)も、高アスペクト比のパターン形成技術が必要となる。出典:Applied Materials(クリックで拡大)前回でも説明したように、アスペクト比(縦と横の比率)のきわめて高いエッチング、すなわち「HARエッチング」が必要となるのは、主に3つの部分である。1つは、メモリセルストリングのチャンネルとなる細長い孔(メモリスルーホール)の形成、もう1つはステアケースの制御ゲートと周辺回路のゲートに対する細長い孔(コンタクト)の形成、最後はメモリセルのゲート形成用スリットの形成である。

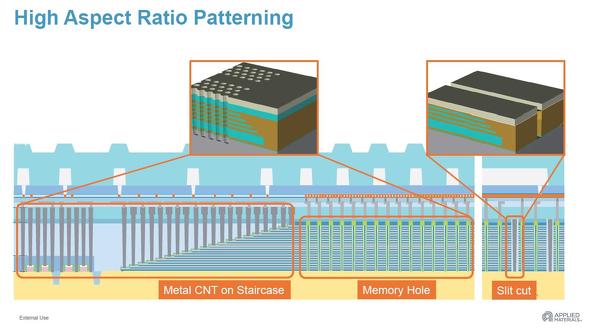

3D NANDフラッシュメモリの断面構造図と、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成部分」(橙色の実線で囲んだ部分、上方は拡大図)。左端は周辺回路のゲートに対するコンタクト、その右がステアケースの制御ゲートに対するコンタクト、中央はメモリセルストリング用のチャンネル(メモリスルーホール)、右端はメモリセルのゲート形成用スリット。出典:Applied Materials(クリックで拡大)

3D NANDフラッシュメモリの断面構造図と、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成部分」(橙色の実線で囲んだ部分、上方は拡大図)。左端は周辺回路のゲートに対するコンタクト、その右がステアケースの制御ゲートに対するコンタクト、中央はメモリセルストリング用のチャンネル(メモリスルーホール)、右端はメモリセルのゲート形成用スリット。出典:Applied Materials(クリックで拡大)これらの細長い孔を形成するためには、2つの新しい技術を駆使する。1つが、前回に説明したハードマスクである。孔開け加工用のエッチングが長時間に及ぶので、レジストのマスクだとレジストが劣化し、寸法が不均一になる。長時間のエッチングに耐えられる、頑丈なハードマスクが欠かせない。

もう1つは、異方性エッチングである。異方性エッチングとは、特定の方向だけを削ることができるエッチング技術のことだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 次世代パワー半導体 「期待の5材料」の現在地

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- Apple新CEOはエンジニア出身 製品開発重視への回帰か