高アスペクト比の細長い孔をハードマスクによって形成:福田昭のストレージ通信(121) 3D NANDのスケーリング(9)

3D NANDフラッシュ製造における重要技術の一つである、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」技術について解説する。

3D NANDフラッシュ製造で必須のHAR孔加工

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュ製造における重要技術(キープロセス)の1つである「ステアケース(Staircase)のパターン形成」技術を解説した。今回は同じくキープロセスの1つである、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成」技術を説明していこう。

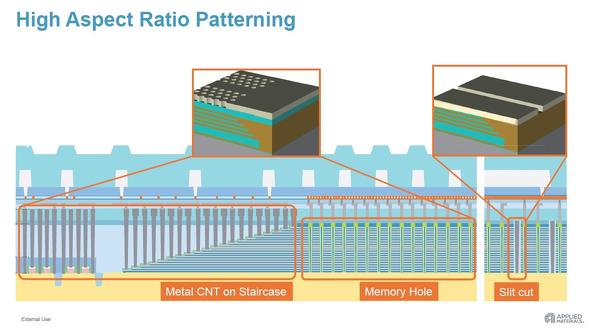

HARのエッチングが必要となるのは、主に3つの部分である。1つは、メモリセルストリングのチャンネルとなる細長い孔(メモリスルーホール)の形成、もう1つはステアケースの制御ゲートと周辺回路のゲートに対する細長い孔(コンタクト)の形成、最後はメモリセルのゲート形成用スリットの形成である。

3D NANDフラッシュメモリの断面構造図と、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成部分」(橙色の実線で囲んだ部分、上方は拡大図)。出典:Applied Materials(クリックで拡大)

3D NANDフラッシュメモリの断面構造図と、「高アスペクト比(HAR:High Aspect Ratio)のパターン形成部分」(橙色の実線で囲んだ部分、上方は拡大図)。出典:Applied Materials(クリックで拡大)レジストマスクとハードマスク

半導体製造プロセスで加工パターンの形成に使う技術は通常、リソグラフィとエッチングである。リソグラフィとはレジスト(感光性樹脂)に光を照射して所望の加工パターンをレチクルから転写する技術である。

エッチングとはシリコン表面あるいはシリコン表面の薄膜を削る技術である。リソグラフィ工程を完了した直後のシリコン表面には、レジストが載ってる部分と、シリコン表面が露出している部分がある。エッチングではレジストをマスク(レジストマスク)とし、シリコン表面が露出している部分を削る。

ここで重要なことは、エッチング中にレジストマスクは少しずつ削られていることだ。もちろんシリコン表面に比べると単位時間当たりに削られる膜厚はわずかである。しかし長時間のエッチングでは、レジストマスクは薄くなるとともに劣化し、マスクとしての効力を発揮できなくなることがある。

3D NANDフラッシュの製造でHAR(高アスペクト比)の細長い孔をエッチングする工程では、エッチング時間が長いので、まさに上記の問題が起こる。レジストマスクは使えない。代わりに使うのが、専用の薄膜をパターニングしてマスクとする「ハードマスク」である。

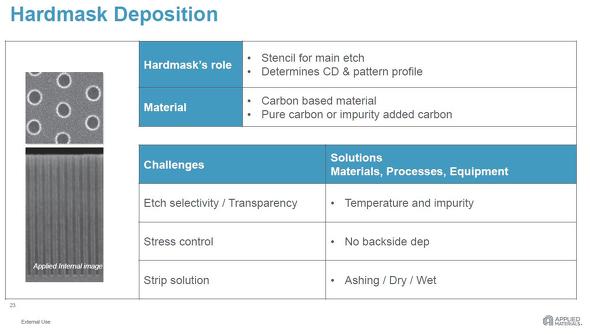

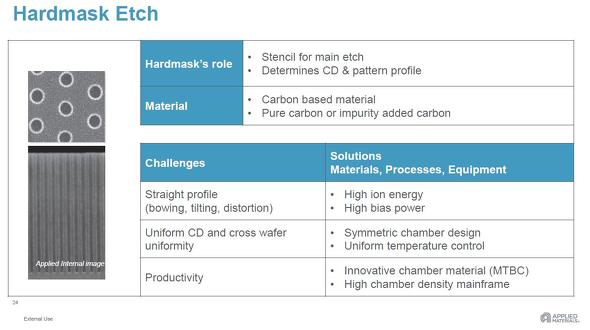

ハードマスクの製造工程は、3つのステップに分かれている。始めはハードマスクとなる薄膜の堆積である。材料にはカーボンをベースとする化合物を使う。次にリソグラフィ技術によって薄膜表面にレジストのパターンを形成する。最後に、このレジストマスクを利用してエッチングによってパターンを形成する。パターン形成後の薄膜が、次にくるHARエッチングのマスクとなる。

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

CypressとSK Hynix System ICが合弁事業

CypressとSK Hynix System ICが合弁事業

Cypress Semiconductorは、SK Hynix System ICとNANDフラッシュメモリの合弁事業を始める。合弁会社は本社を香港に置き、SK Hynix System ICが60%、Cypressが40%の株式を保有する。 125℃動作を保証し5V対応、64kビットFRAM

125℃動作を保証し5V対応、64kビットFRAM

富士通セミコンダクターは、125℃までの動作温度を保証し、最大5.5Vの電源電圧に対応する64kビットFRAM(強誘電体メモリ)「MB85RS64VY」を開発した。 3D NANDフラッシュメモリの断面構造と製造工程

3D NANDフラッシュメモリの断面構造と製造工程

2018年5月に開催された国際会議「IMW」で行われたセミナー「3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望」の概要をシリーズで紹介している。今回は、3D NANDフラッシュメモリの断面構造と、メモリセルアレイの製造工程を解説しよう。 メモリセルの制御ゲートをワード線に引き出すステアケース

メモリセルの制御ゲートをワード線に引き出すステアケース

今回は、「ステアケース(Staircase)のパターン形成」技術について解説する。特に注目したいのが、ステアケースのパターン形成を短時間で行える「トリム」技術だ。 2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm技術で試作した40Mビット埋め込みMRAM(前編)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。 記憶容量と書き換え回数から最適な埋め込みメモリを選択

記憶容量と書き換え回数から最適な埋め込みメモリを選択

半導体デバイス技術に関する国際会議「IEDM」で行われたセミナー「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」の概要を今回からシリーズで紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 全固体電池の製造プロセス簡素化、東北大が新手法

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める