アトミックレイヤーエッチングとドライエッチング技術の未来展望:湯之上隆のナノフォーカス(6) ドライエッチング技術のイノベーション史(6)(4/5 ページ)

SACの問題

ゲート電極とコンタクトホールのリークを無くすためには、なるべく保護膜のSiNを厚く成膜したい。ところが、SiNが厚過ぎると、コンタクトホールの底面積が小さくなり、コンタクト抵抗が増大するという問題が起きる。

コンタクト抵抗増大を避けるには、コンタクトホールの底面積を大きくすることが有効であり、そのためにはゲート電極を保護するSiN膜を薄くしたい。ところが、薄くし過ぎると、ゲート電極とコンタクトホールの間でリークが起きやすくなる。

要するに、コンタクト抵抗とリークはトレードオフの関係にあり、両者を同時に満足するのが困難である。しかし、トランジスタの高集積化のためには、なるべくトランジスタ間の距離を縮めたいという要求がある。

この問題の解決には、なるべくSiN膜を削らないSiO2エッチング、つまり、SiNに対する選択比が高いSiO2エッチング技術が必要である。そして、この厄介な問題を、SiO2のALEが解決したのである。

SACに適用されたALE

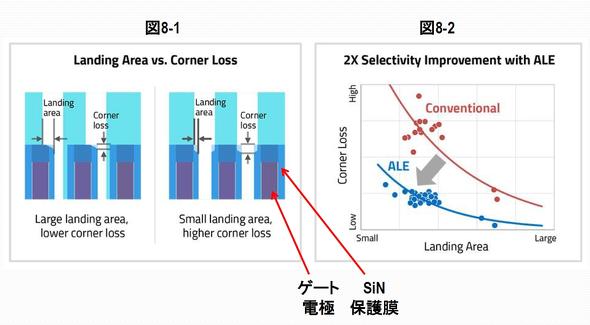

米Lam ResearchがSACプロセスにALEを適用したときの実験結果を図8に示す。

図8-1では、コンタクトホールを開口する際、ゲート電極の保護膜SiNが露出する横方向の面積を“Landing area”、保護膜が縦方向に削れる寸法を”Corner Loss“と定義している。

図8-1の左図のように、Landing areaが大きい場合は、Corner Lossは小さくなるが、コンタクトホールの底面積が小さくなってしまう。一方、図8-1の右図のように、Landing areaが小さい場合は、コンタクトホールの底面積を大きくできるが、Corner Lossが大きくなってしまう。

望ましくは、Landing areaもCorner Lossも小さくし、コンタクトホールの底面積を大きくしたいが、Landing areaとCorner Lossはトレードオフの関係にある。そのため、図8-2に示すように、Conventionalなドライエッチングでは、その解決が困難だった。

ところが、ALEを用いた場合、Conventionalなエッチングに比べて、Landing areaもCorner Lossも同時に小さくできることが分かった。これは、ALEにより、SiNに対する高選択SiO2エッチングが可能になったことを意味している。

その結果、同じデバイス構造なら、コンタクトホールの底面積を大きくすることができる。または、Conventionalなドライエッチングを用いる場合よりも、トランジスタ間を狭くし、集積度を増大することが可能になる。

このLam Researchの技術は、先端ロジック半導体メーカーに使われた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増