アトミックレイヤーエッチングとドライエッチング技術の未来展望:湯之上隆のナノフォーカス(6) ドライエッチング技術のイノベーション史(6)(3/5 ページ)

ALEの原理

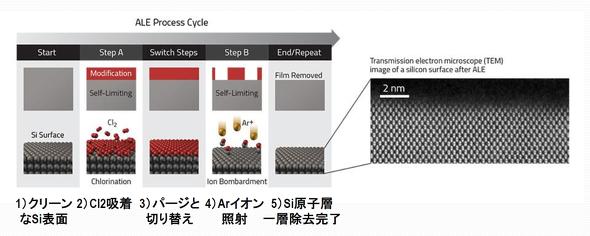

シリコンのALEの事例を、図5を用いて説明する。

1)ウエット洗浄を行って、シリコン表面をクリーンにする。

2)ラジカルとして、塩素をシリコン表面に吸着させる。

3)塩素をパージし、ステップを切り替える。

4)Arイオンを照射すると、反応性イオンエッチングにより、SiCl4が揮発する。

5)シリコン原子一層分の除去が完了する。

このとき、シリコンなどの導電膜では、2)のラジカル吸着過程で、塩素が原子一層分しか吸着しない。この現象を、セルフリミッティングという。この効果により、Arイオンを照射すると、シリコン原子が一層分だけエッチングされる。

一方、SiO2などの絶縁膜では、2)でCFxラジカルを吸着させるが、セルフリミットがかからず、時間とともにCFxラジカルがどんどん堆積してしまう。そのため、SiO2のALEにおいては、CFxラジカルの吸着の時間などを、精密に制御しなくてはならない。

導電膜と絶縁膜では、このようにセルフリミッティングに大きな違いがあり、実用化するには導電膜のALEの方がやりやすいと思われていた。ところが、実際に量産適用されたのは、セルフリミッティングがかからないSiO2のALEだった。そのアプリケーションは、先端ロジック半導体のセルフアラインコンタクト(Self-Aligned Contact、SAC)という工程だった。

SACとは何か

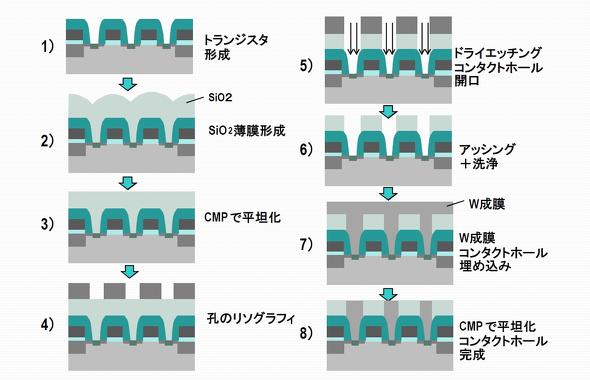

トランジスタを形成した後、密集したトランジスタ間に、次のようなプロセスフローでコンタクトホールを形成する(図6)。

1)トランジスタを形成する。

2)SiO2膜を成膜し、トランジスタを埋め込む。

3)CMPによりSiO2膜を平たん化する。

4)リソグラフィにより、孔のレジストパターンを形成する。

5)ドライエッチングにより、コンタクトホールを開口する。

6)レジストを除去し、孔底を洗浄する。

7)タングステン(W)を成膜する。

8)不要なWを除去する。これで、Wで埋め込まれたコンタクトホールが完成する。

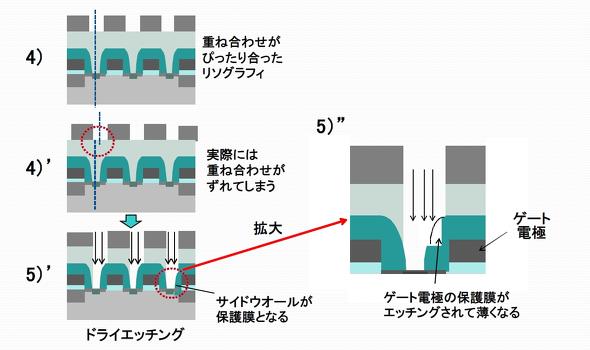

ところが、4)の孔のレジストパターン形成の際、レジストパターンの中心が、二つのトランジスタの中心に合うとは限らない(図7)。というより、現実には、必ず、合わせずれが起きる。

SACとは、このような合わせずれが起きても、ゲート電極をSiNが保護することにより、コンタクトホールのドライエッチングの際に、ゲート電極が露出しないように工夫したプロセスである。

もし、ゲート電極が露出すると、Wで埋め込まれたコンタクトホールとゲート電極が、電気的に接触(つまりリーク)してしまい、トランジスタ動作に不具合をきたすことになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増