メモリホールにおけるエッチングと成膜の難度を軽減する2つの手法:福田昭のストレージ通信(128) 3D NANDのスケーリング(14)(1/2 ページ)

3D NANDフラッシュメモリの高密度化と大容量化を実現する手法について、技術的な難度を低減する2つの方法を解説する。

セルストリングを2段階に分けて製造

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前回では、3D NANDフラッシュメモリの高密度化と大容量化をけん引する基本的な手法を紹介した。それは「ペア薄膜の積層数を増やすことによって、セルトランジスタ数を垂直方向に増やすこと」である。

ただしこの手法には「セルトランジスタの数が増えるとメモリホールのエッチングと成膜における技術的な難度が増加する」という根本的な問題がある。そこで今回は、技術的な難度を軽減する、2つの手法を解説していく。

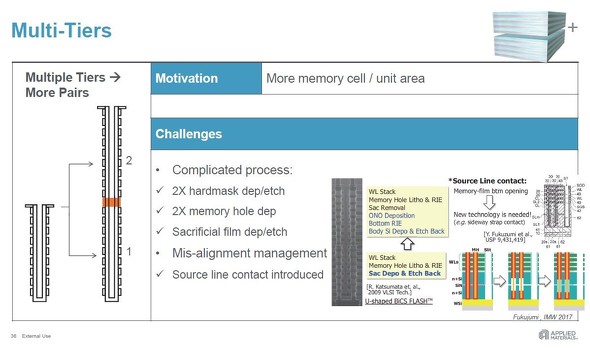

最初に紹介するのは、セルストリング(セルトランジスタの垂直方向の連なり)を複数の段階に分けて製造する手法である。「マルチティア(Multi-Tiers)」あるいは「マルチスタック」と呼ばれている。

「マルチティア」では、セルストリングを一括して製造するのではなく、2つ以上のティア(スタック)に分けて製造する。例えば64個のセルトランジスタを垂直方向に積層する場合、まず32個のセルトランジスタによるセルストリング(ティア)を製造する。32ペアの薄膜に対してメモリホールのエッチングと電荷捕獲膜およびチャンネルの成膜を実施し、セルストリングを作る。次に再び32個のセルトランジスタによるティアを製造する。「2ティア」あるいは「2スタック」と呼ばれる構成である。

マルチティアの良い点は明らかだ。エッチングと成膜の難度が下がる。ただし課題も当然ながら、存在する。まず、上下のティアの位置合わせ精度が問題になる。また上のティアを製造しているときに、下のティアに何らかのダメージを与える可能性がある。そして製造工程が2段階となるので、生産のスループットが低下する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める