東京大学とTSMCがアライアンス締結:TSMCが東大にシャトルサービスなどを提供(2/2 ページ)

ゲートウェイ機能と共同技術研究で協業

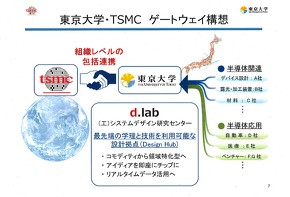

締結したアライアンスは「デザインを機能的なチップに変換するゲートウェイの役割を担う」(両者)と説明する。具体的には、日本国内の半導体ユーザー企業、半導体デバイスメーカー、半導体製造装置/材料メーカーのアイデアやニーズを、東京大学d.labに集約。そうしたニーズやTSMCのロードマップを互いに共有しながら「最先端プロセスを活用するためのハードルを下げ、(日本の産業界が求める)領域特化型チップ、用途特化型チップなどをTSMCで即座に試作するようにする」(東京大学副学長藤井輝夫氏)。TSMCは「シャトル試作サービスを東京大学に提供し、d.labのチップ試作を先進プロセスで行う」としている。

d.labセンター長を務める黒田忠広氏は「エネルギー効率を高める必要があり、そのためには領域に特化したデバイスの開発が必要になる。だが、領域特化デバイスの開発には、汎用デバイスのような大きなリソースはかけることができない。そこで、d.labでは、消費電力を10分の1のデバイスを、10分の1の開発リソースで実現することが目標」と語った。

またアライアンスでは、こうした日本産業界とTSMCの最先端プロセス製造をつなぐゲートウェイ機能以外にも、先進半導体技術の共同研究を実施する方針。「次世代の半導体デバイスビジョンと予測されうる諸課題を共有し、今後共同研究として取り上げるべき研究分野について議論していく。年1〜2回程度の定期的な設計技術を含めた分野横断型のシンポジウムを開催する」とした。

TSMCでR&Dコーポレートリサーチ担当バイスプレジデントを務めるH.-S.Phillip Wong氏は、「TSMCは引き続き、トランジスタの微細化を進めていく。2020年には5nm技術の量産をスタートし、その後3nmへと進めていく。こうした平面での微細化、高密度化に加え、3次元構造技術を用いてシステムとしての高密度化も達成していきたい。将来に向けた技術開発には、材料、物理、化学などのさまざまなノウハウが必要で、こうした知識を持つ東大とのアライアンスに期待をしている」と述べた。

関連記事

航空電子と東大生研が連携研究協力協定を締結

航空電子と東大生研が連携研究協力協定を締結

東京大学生産技術研究所と日本航空電子工業は2019年3月22日、産学連携研究協力協定を締結したと発表した。同協定に基づき、両者は今後3年間にわたって、次世代モビリティ、IoT(モノのインターネット)社会の実現および、研究開発人材の育成を目的に包括的な共同研究を行う。 MediaTekがASIC事業強化、7nmと豊富なIPで勝負

MediaTekがASIC事業強化、7nmと豊富なIPで勝負

台湾MediaTekは、ASIC事業を強化する。システムの技術革新につながる最新IPコアの開発などにも取り組む。 半導体製造プロセスは継続的な進化を

半導体製造プロセスは継続的な進化を

EUV(極端紫外線)リソグラフィの開発プロセスは、長期にわたって難しい道のりを進んできた。EUV開発については、EUVの新しいパターニング性能を採用するかしないかによって、半導体チップ製造プロセスが将来的にどのような技術になるのかを、一歩引いた所から検討する必要があるのではないだろうか。 TSMCがEUV適用7nmプロセスを商用化

TSMCがEUV適用7nmプロセスを商用化

世界最大のファウンドリーであるTSMCは2019年10月7日(台湾時間)、「業界で初めてEUV技術を商用化」(同社)し、EUVを採用した7nmプロセス「N7+」を発表した。同社は報道向け発表資料の中で、「当社は現在、複数の顧客企業からのN7+プロセスへの需要に対応すべく、生産能力を迅速に拡大しているところだ」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待