多ピンと小型・薄型・低コストを両立させるFO-WLPの組み立て技術:福田昭のデバイス通信(217) 2019年度版実装技術ロードマップ(28)(1/2 ページ)

パッケージの組み立てプロセス技術を紹介している。今回は、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。

多ピン向け薄型パッケージの主役となったFO-WLP

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第28回である。

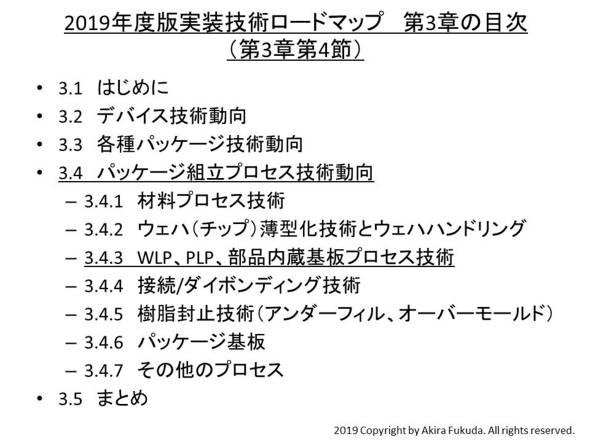

本シリーズの第23回から、第3章「電子デバイスパッケージ」の概要を紹介している。「電子デバイスパッケージ」は第1節から第5節までの5つの節によって構成される。「3.1 はじめに」「3.2 デバイス技術動向」「3.3 各種パッケージ技術動向」「3.4 パッケージ組立プロセス技術動向」「3.5 まとめ」である。前回から、第3章第4節「3.4 パッケージ組立プロセス技術動向」の概要をご紹介している。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第23回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第23回から第3章「電子デバイスパッケージ」(プログラムの7番)の概要を解説している。出典:JEITA(クリックで拡大)前回は、第1項「3.4.1 材料プロセス技術」の内容である、代表的な半導体パッケージの組み立てフローを説明した。具体的には、QFN(Quad Flat Non-leaded package)、FBGA(Fine-pitch BGA)/BGA(Ball Grid Array)、WL-CSP(Wafer Level-Chip Scale Package)、FO-WLP(Fan Out-Wafer Level Package)を取り上げた。

今回はロードマップの第3項「3.4.3 WLP、PLP、部品内蔵基板プロセス技術」に記述された、FO-WLPの組み立て工程を解説していく。FO-WLPは、数多くの入出力端子を収容可能な多ピンパッケージでありながら、小型・薄型・低コストを両立させるという優れた性質を備える。FO-WLPの組み立て工程には、いくつかの手法が存在する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表