早くもTSMCの代表的なプロセスに? 7nm技術:採用チップも順調に拡大(1/2 ページ)

2019年に発表された多くのSoC(System on Chip)が7nmプロセスを採用している。だが、「7nm」が全て同等というわけではない。本稿では、現在高い評判を得ているSoCについて要約する。下表に、それらのSoCに用いられているプロセスをまとめた。

2019年に発表された多くのSoC(System on Chip)が7nmプロセスを採用している。だが、「7nm」が全て同等というわけではない。本稿では、現在高い評判を得ているSoCについて要約する。下表に、それらのSoCに用いられているプロセスをまとめた。

| プロセス | 製造している代表的なSoC/CPU | |

|---|---|---|

| TSMC | N7(N7FF) | AMD「Zen 2」、HiSilicon「Kirin 990」、Apple「A12」、Qualcomm「Snapdragon 855」 |

| N7P | Qualcomm「Snapdragon 865」、Apple「A13」、MediaTek「Dimensity 1000L」 | |

| N7+ | HiSilicon「Kirin 990 5G」 | |

| Samsung Electronics | 8LPP | Samsung「Exynos 9820」、Qualcomm「Snapdragon 730」 |

| 7LPP | Samsung「Exynos 9825」 | |

TSMCは2019年4月に7nmプロセスの量産を開始した。同社の計画では、7nmは比較的長期間にわたる完全なプロセスノードである。前世代は16nmだった。10nmは短期間での移行が計画された。上の表では、TSMCの最初の7nmプロセスは「N7(またはN7FF)」である。このプロセスは、Qualcommの「Snapdragon 855」、Huaweiの「Kirin 990」、AMDの「Zen 2」といったSoC製品に幅広く用いられている。

TSMCでは、7nmプロセスを用いて製造すると、16nmに比べてチップの処理性能が35〜40%増加し、消費電力は65%削減されると主張する。だが、実際に製造したチップでこれらの向上を実現するのは難しいはずだ。

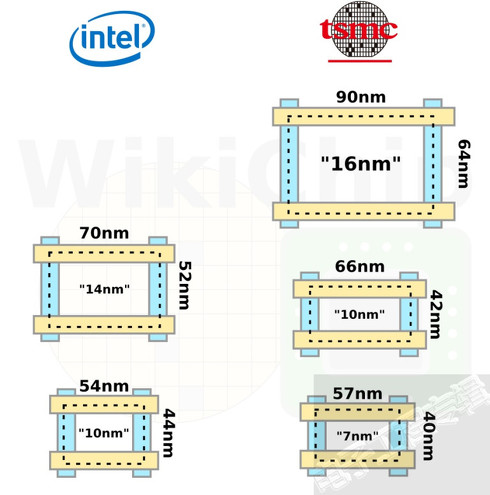

TSMCのN7は現在でも193nm ArF(フッ化アルゴン)液浸リソグラフィを用いている。これは、Samsungの「7LPP(7nm Low Power Plus)」とはかなり異なる技術だ。N7プロセスでは、トランジスタゲートピッチが57nmに、配線ピッチ(MMP:Minimum Metal Pitch)が40nmに低減された。下の図は、TSMCの前世代品とIntelのプロセスのゲートピッチ、配線ピッチを簡単に比較したものである。

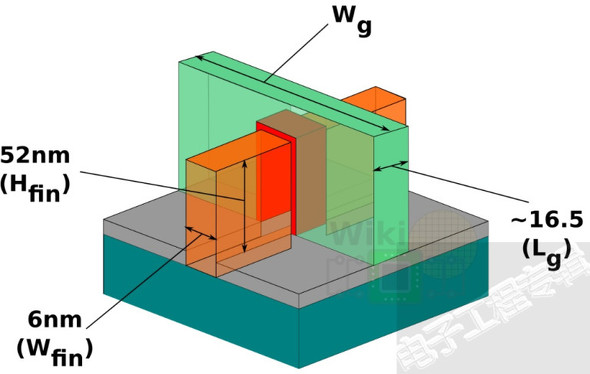

単一のトランジスタに関して言えば、N7トランジスタのトレンチ接合部は、以前のW(タングステン)の代わりにCo(コバルト)を使用しているため、接合部の抵抗を50%低減できるという。また、フィンの幅(Wfin)と高さ(Hfin)は理論的な観点から変更する必要がある。フィンの幅を小さくすると、実質的にチャネルが狭くなる。フィンの高さを高くすると、断面全体を比較的効果的に維持できるので、寄生効果を低減し、実効電流(Ieff)や実効キャパシタンス(Ceff)などの特性を強化できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

出典:WikiChip

出典:WikiChip