早くもTSMCの代表的なプロセスに? 7nm技術:採用チップも順調に拡大(2/2 ページ)

N7プロセスの2つの種類

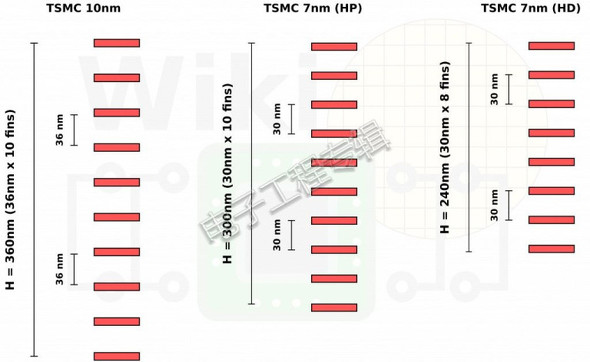

TSMCのN7プロセスには実際は、低消費電力高密度(HD)と高性能(HP)に対応した2つがある。上記で言及しているのは、N7 HDプロセスについてである。これら2つの異なるセルソリューションは、フィンピッチはともに30nmだが、ゲートピッチは前者が57nmで、後者が64nmである。

標準セルに関しては、これら2つのソリューションのセルの高さは240nm(6トラック、より一般的に言えば6T)と300nm(7.5T)である。HPは10フィンで、HDは8フィンである。HP高性能セルは、リーク電流が少し高いが、10〜13%高い実効駆動電流(Ieff)を実現している。

HPとHDでは、トランジスタ密度も異なる。HD低消費電力N7のトランジスタ密度は91.2MTr/mm2(「MTr/mm2」は、1mm2当たり100万個のトランジスタが集積されているという意味)で、HP N7では65MTr/mm2である。

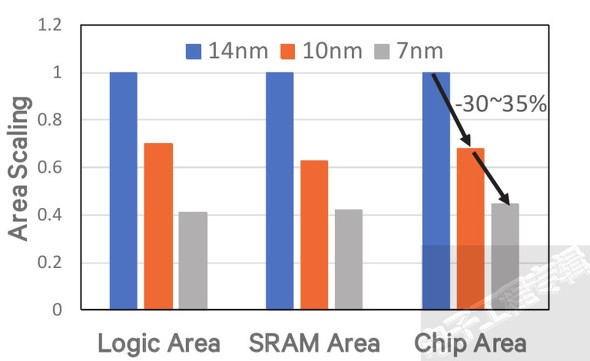

これらの数値が分からない場合は、特定のIP(Intellectual Property)または製品と比較することで大まかな数字把握できる。Qualcommは2019年の「VLSIシンポジウム」で、「N7プロセスによって、『Snapdragon 855』はロジック回路とSRAM領域、それらを含めたチップ領域を(Samsung Electronicsの10nmプロセスを適用した前世代の『Snapdragon 845』と比べて)30〜35%縮小した」と述べていた。

N7は、TSMCにとって最初の7nmプロセスである。TSMCは既に7nmの第2世代となるN7Pを発表している。N7PはN7をグレードアップしたもので、N7同様、ArF液浸リソグラフィを使用しており、IPはN7と完全な互換性を確保している。

Appleの「iPhone 11」シリーズに搭載されている「A13」は、N7Pプロセスを採用している。2020年に量産される予定のQualcomm「Snapdragon 865」も同プロセスで製造される。

EUVも導入

N7+とN7Pは異なる。N7+では、複数の主要なレイヤーにEUV(極端紫外線)リソグラフィを用いている。2019年第2四半期に量産が開始されている。TSMCによれば、N7+は、N7Pに比べてトランジスタ密度が1.2倍になるという。消費電力が同じ場合、処理性能はN7+は10%向上し、処理性能が同じ場合は、N7+の消費電力は15%減になるとしている。つまり、N7+はN7Pよりも高性能だということだ。TSMCは、N7+の歩留まりは基本的にN7と同等レベルだという。

【翻訳:青山麻由子、滝本麻貴、編集:EE Times Japan】

関連記事

微細配線が可能なFO-WLPの組み立て技術

微細配線が可能なFO-WLPの組み立て技術

前回に続き、FO-WLP(Fan Out-Wafer Level Package)の組み立て工程を解説する。今回は、微細配線を形成可能なFO-WLPを取り上げる。 製造装置市場にジワリと進出する韓国、ローカルでは独占分野も

製造装置市場にジワリと進出する韓国、ローカルでは独占分野も

製造装置市場における企業別シェアを分析する。分野によっては韓国企業が着実にシェアを上げている。収束する気配のない日韓貿易戦争が続く中、日本企業は、韓国市場で失うであろうシェアを別の地域で補う必要がある。 TSMCがEUV適用7nmプロセスを商用化

TSMCがEUV適用7nmプロセスを商用化

世界最大のファウンドリーであるTSMCは2019年10月7日(台湾時間)、「業界で初めてEUV技術を商用化」(同社)し、EUVを採用した7nmプロセス「N7+」を発表した。同社は報道向け発表資料の中で、「当社は現在、複数の顧客企業からのN7+プロセスへの需要に対応すべく、生産能力を迅速に拡大しているところだ」と述べている。 5nm/7nmチップの需要を後押しするのは「5G」

5nm/7nmチップの需要を後押しするのは「5G」

TSMCは、「5G(第5世代移動通信)開発の世界的な加速に伴って、5nmと7nmチップの需要が以前の予測よりも増加する」と予想している。 2019年の半導体売上高ランキング、Intelが首位奪還

2019年の半導体売上高ランキング、Intelが首位奪還

Gartnerは2020年1月14日(米国時間)、2019年の世界半導体売上高が、2018年から11.9ポイント下がって4183億米ドルになったと発表した。ベンダー別の売上高では、Intelが2016年以来3年ぶりに首位を奪還した。 Intelが3つの次世代パッケージング技術を明らかに

Intelが3つの次世代パッケージング技術を明らかに

Intelは、米国カリフォルニア州サンフランシスコで2019年7月9〜11日の日程で開催されている「SEMICON West 2019」に合わせて行われたイベントにおいて、3種類のパッケージング技術に関する同社のロードマップを初めて明らかにした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増