FinFETやGAAにも適用可能なエアスペーサー形成技術:VLSIシンポジウム 2020(1/2 ページ)

オンラインで開催された半導体デバイス/回路技術に関する国際会議「VLISシンポジウム 2020」(2020年6月15〜18日/ハワイ時間)で、IBM Researchの研究グループは先端CMOSにエアスペーサーを導入する技術を発表した。

オンラインで開催された半導体デバイス/回路技術に関する国際会議「VLISシンポジウム 2020」(2020年6月15〜18日/ハワイ時間)で、IBM Researchの研究グループは先端CMOSにエアスペーサーを導入する技術を発表した。

IBM Researchが開発した技術は、トランジスタゲート周辺にエアースペーサーを形成するもので、あらゆるトランジスタ構造に適用できる。さらに、低消費電力化と高性能化も図ることができるとする。研究グループは実際、このエアースペーサーを、7nmプロセスを用いたFinFETに適用し、5nmプロセスにスケーリングした場合よりも高性能化と低消費電力化を実現できることを実証した。

一方、CEA- Leti(フランス原子力庁の電子情報技術研究所)の研究グループは今回、FinFET技術の代替として、新たにナノシートを7層積層したGAA(Gate All Around)NS(ナノシート)トランジスタアーキテクチャを開発したという。チャネル幅は15nm〜85nm。CEA- Letiは、その研究成果についてまとめた論文を発表している。

エアースペーサー、5nmプロセスへのスケーリングよりも優れた性能を7nmで実現

IBM Researchは、FinFETやナノシートデバイスアーキテクチャなど、さまざまな種類のトランジスタアーキテクチャとの互換性を備えたエアースペーサー形成技術を発表した。

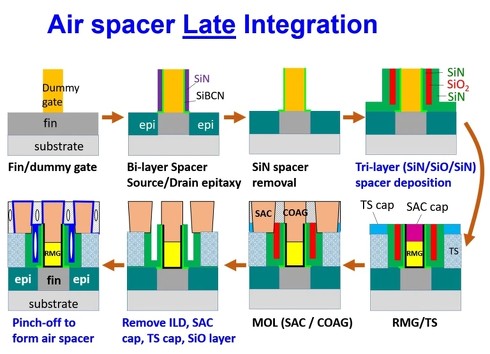

同社の研究グループは、論文「Improved Air Spacer Co-Integrated with Self-Aligned Contact (SAC) and Contact Over Active Gate (COAG) for Highly Scaled CMOS Technology(高性能エアースペーサー:スケーリングが進むCMOS技術向けに自己整合コンタクト(SAC)とContact Over Active Gate(COAG)を統合)」の中で、この新しいエアースペーサーについて、その誘電率を落とすことにより、CMOSデバイス特性に影響を及ぼす重要な要素の1つである実効容量を15%低減できる他、性能向上と消費電力量削減を同時に実現できることなど、詳細を説明している。SACとCOAGに関しては、FinFET技術でも適用され、トランジスタの設置面積やスタンダードセルを縮小するなど貢献しているが、エアースペーサーとSAC/COAGの統合は、非常に難しい課題である。

スペーサーは、トランジスタ内部のゲートとソース/ドレインのコンタクトとの間の絶縁層であり、基本的に電子スイッチとして機能する。ゲートがオンの時、電気はソースからドレインに流れるため、ゲートがバルブの役割を担う。スペーサーは、ゲートが電気の流れだけを制御して、ゲートとソース/ドレインが電気的に絶縁された状態を確実に維持できるようにする。ゲートはスペーサーなしに、バルブとしての機能を果たすことはできない。

IBMの研究グループは、今回の高性能エアースペーサーについて、「寄生容量を低減することで、高性能CMOS技術のエネルギー効率と性能の向上を実現できる手法である」と位置付けている。論文には、エアースペーサーを形成するための新しいプロセスや、電子デバイスの低消費電力化と高性能化を実現するための実践的な手法などが記されている。

実際に、新しいエアースペーサーモジュールを7nm FinFETに適用すれば、膨大なコストを要する問題山積の5nmプロセスへのスケーリングを実行する場合よりも、はるかに高性能化することができるという。研究グループは、「今回われわれが開発した新技術は、今後数年のうちに、FinFETやナノシートトランジスタに適用されるようになるだろう」と期待しているようだ。

IBMの研究グループメンバーで、今回のプロジェクトのプレゼンを務めたKangguo Cheng氏は、EE Timesのインタビューに応じ、「われわれが前回、2016年に発表したエアースペーサー『AS-Early(air spacer early)』は、middle-of-line(MOL)コンタクト形成前の初期段階のデバイス作製において形成されたものだ。AS-Earlyは、CMOSフローに簡単に挿入することができるが、7nmプロセス以降に微細化が進むと、問題が生じる。例えば、7nmプロセス以降でCMOSの標準的なセルサイズを縮小するための重要な技術要素であるCOAGとの互換性がないことなどが挙げられる」と述べる。

「われわれが発表したエアースペーサー手法では、エアースペーサーは、middle-of-lineコンタクト形成後の後期段階のデバイス作製において形成される。この新手法は、SACとCOAGとの完全な互換性を実現するため、AS-Earlyが抱える微細化の問題を克服することが可能だ」(同氏)

さらに同氏は、「他にも、この2つの手法が明らかに異なっている点としては、AS-Earlyはプレーナ/FinFETデバイスの寄生容量を低減できるが、ナノシートやナノワイヤデバイスなどの新しいGAAデバイスに対してはそれほど効果がないということが挙げられる。一方、今回カンファレンスで発表した新しい手法は、GAAも含めたあらゆる種類のデバイスアーキテクチャに対して優れた効果を発揮する」と続けた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

IBMのKangguo Cheng氏

IBMのKangguo Cheng氏