EE Times Japan >

プロセス技術 >

FinFETやGAAにも適用可能なエアスペーサー形成技術:VLSIシンポジウム 2020(2/2 ページ)

» 2020年07月03日 11時30分 公開

[Nitin Dahad,EE Times]

7層構造のナノシートGAAトランジスタ

CEA-Letiは、FinFET技術の代替となる、新しいGAAナノシートデバイスの作製デモを披露した。低消費電力、高速動作によるデータ収集と処理が可能な、スマートフォンやノートPC、モバイルシステムなどのHPCアプリケーションをターゲットとする。

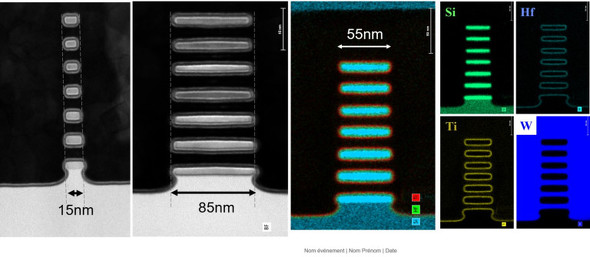

研究グループが今回作製した、7層のシリコンチャンネルを積層したGAA NSトランジスタは、チャネル幅が15nm〜85nmで、既存の最先端技術と比べて2倍以上の性能を実現するという。その研究成果に関する詳細は、論文「7-Levels-Stacked Nanosheet GAA Transistors for High Performance Computing(HPC向け7層積層GAA NSトランジスタ)」にまとめられている。

論文の著者の1人であるCEA-Letiの科学者、Sylvain Barraud氏は、「置換メタルゲート、インナースペース形成、SACを用いて作成した7層構造の積層ナノシートGAAトランジスタは、極めて高い電流駆動能力(Vdd=1Vで3mA/μm)を持つ優れたゲート制御性を示し、2層構造のナノシートGAAトランジスタと比較して、ドレイン電流が3倍向上している」と説明した。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

「VLSIシンポジウム2020」は初のオンライン開催に

「VLSIシンポジウム2020」は初のオンライン開催に

2020年6月15〜18日(以下、特に記載がない限り全てハワイ時間)に開催される半導体デバイス/回路技術に関する国際会議「VLSIシンポジウム 2020」。本来は米国・ハワイで開催される予定だったが、新型コロナウイルス感染症(COVID-19)の影響で、初のオンライン開催となる。VLSIシンポジウム委員会は2020年5月20日、記者説明会をオンラインで開催し、概要を説明した。 EUVを適用した小型SRAMセル、imecらが発表

EUVを適用した小型SRAMセル、imecらが発表

フラッシュメモリの発明者が率いる新興企業Unisantis Electronics Singapore(以下、Unisantis)が、ベルギーの研究機関imecと共同開発を進めてきた、小型SRAMセルに関する発表を行った。 アトミックレイヤーエッチングとドライエッチング技術の未来展望

アトミックレイヤーエッチングとドライエッチング技術の未来展望

ドライエッチング技術のイノベーション史をたどるシリーズの最終回は、アトミックレイヤーエッチング技術に焦点を当てる。さらに、今後の展望についても考察する。 誰がドライエッチング技術を発明したのか

誰がドライエッチング技術を発明したのか

前回に引き続き、ドライエッチング技術におけるイノベーションの歴史を取り上げる。今回は、ドライエッチング技術の開発を語る上で欠かせない、重要な人物たちと、彼らが発明した技術を紹介する。 パナと日本IBMが半導体製造装置分野で協業

パナと日本IBMが半導体製造装置分野で協業

パナソニックと日本IBMが、半導体製造装置分野で協業する。パナソニックが製造、販売するプラズマダイサーなどの半導体後工程製造装置の価値を高めるソフトウェアなどをパナソニックと日本IBMで共同開発し、パナソニックが製造装置ともに提供する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「AI特需」の恩恵届かぬ日本企業 Gartnerが見る2026年半導体市場

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- シリコンフォトニクスと先進パッケージの統合が描く未来

Special SitePR

あなたにおすすめの記事PR