半導体パッケージ基板の技術ロードマップ:福田昭のデバイス通信(263) 2019年度版実装技術ロードマップ(71)(2/2 ページ)

ビルドアップ構造の量産基板は配線幅/間隔で10μm/10μmがほぼ限界

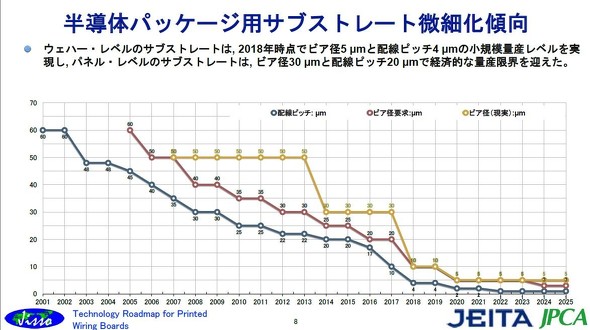

半導体パッケージ基板は、プリント配線板の微細化をけん引してきた。しかしここに来て微細化の壁に突き当たりつつある。微細化をけん引していたのは過去にはリジッド配線板プロセスとセラミック基板プロセスだった。最近はビルドアップ配線板が微細化を主導してきた。

経済性を考慮すると、配線幅(導体幅)/間隔で10μm/10μmが現在のところ、ほぼ量産の限界だとされる。さらなる微細化をけん引するのは従来のプリント配線板製造技術ではなく、半導体製造技術だと考えられる。

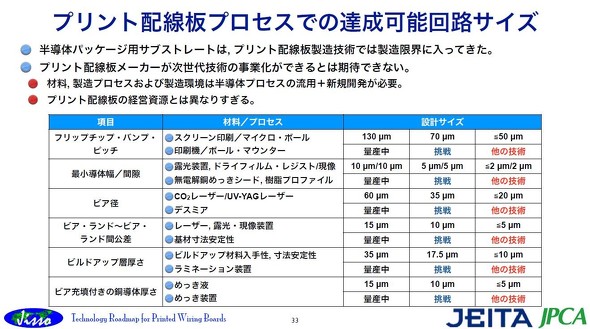

ただし、ある程度のコスト増を許容すると、ビルドアップ構造を含めたプリント配線板技術でもいくらかの微細化と高密度化が見込める。例えばフリップチップのバンプピッチでは130nmピッチが量産中であり、次の70nmピッチが従来技術の改良による目標となる。配線幅(導体幅)/間隔では10μm/10μmが量産中であり、次の目標は5μm/5μmである。ビア径は60μmが量産中であり、35μmが次の目標だ。

次世代の微細配線製造技術で0.5μm/0.5μmを目指す

さらに微細化と高密度化を進めるには、次世代の微細配線板製造技術が必要とされる。その候補を挙げると、「ビルドアップ基板と薄膜インターポーザーの組み合わせ」「ガラス基板(ガラスサブストレート)」「ウエハーレベル基板(シリコン基板)」「緩やかな配線ピッチのシリコンインターポーザー(ラフピッチ・シリコンインターポーザー)」「微細な配線ピッチのシリコンインターポーザー(ファインピッチインターポーザー)」がある。

これらの次世代技術によって配線幅(導体幅)/間隔で2μm/2μm、さらには0.5μm/0.5μmという極めて微細な配線の実現を目指す。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

筐体や衣服などとの融合を目指す新世代の配線板技術

筐体や衣服などとの融合を目指す新世代の配線板技術

今回は、異なる製造技術によって付加価値を高める技術「ストレッチャブル配線板」「コンフォーマブルエレクトロニクス」「テキスタイルエレクトロニクス」の3つを取り上げる。 小型化と薄型化、多機能化を後押しする部品内蔵基板

小型化と薄型化、多機能化を後押しする部品内蔵基板

今回は、新世代のプリント配線板を代表する「機能集積基板」の概要を解説する。半導体チップや受動部品などを内蔵することで複数の機能を持たせた基板である。 プリント配線板の性能を大きく左右する絶縁材料

プリント配線板の性能を大きく左右する絶縁材料

プリント配線板では多種多様な絶縁基材が使われる。新世代のプリント配線板が採用した新しい絶縁基材について解説する。 変革期を迎えたプリント配線板技術

変革期を迎えたプリント配線板技術

今回から、第5章「プリント配線板」の概要を解説していく。まずは伝統的なプリント配線板の用語と製造方法を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長