5G Open RAN向けのアクセラレーターカード Xilinx:低コスト化と省電力化を実現

Xilinxは2020年9月15日(米国時間)、5G(第5世代移動通信)で注目されているオープン無線アクセスネットワーク(Open RAN)向けにテレコムアクセラレーターカード「T1」を発表した。

Xilinxは2020年9月15日(米国時間)、5G(第5世代移動通信)で注目されているオープン無線アクセスネットワーク(Open RAN)向けにテレコムアクセラレーターカード「T1」を発表した。Open RANの分散型ユニット(DU)や仮想ベースバンドユニット(vBBU)で使用する製品で、フロントホール終端の機能と、L1の負荷を下げる機能(L1オフロード機能)を高速化する。これによって、DUやvBBU内のプロセッサのコア数を削減できるので、システム全体の低コスト化、低消費電力化につながる。既に量産出荷を開始している。

Open RANへの関心が高まる

XilinxがT1を開発した背景には、Open RANに対応した5G向け通信機器への需要の高まりがある。Xilinxのワイヤードおよびワイヤレスグループで製品計画およびマーケティング担当ディレクターを務めるMike Wissolik氏は、「Xilinxはこれまでも5G向けに多くの製品を市場に投入しているが、2019年の終わりから2020年の初めにかけて、Open RAN向けの製品はあるかと尋ねられることが多くなった」と語る。5Gは、自動車やVR(仮想現実)、ゲームといった新しいアプリケーションでの活用が期待されているが、こうしたアプリケーションでは、通信機器が特定のベンダーに固定されているとソフトウェアの実装や運用が難しい。「ベンダーによる制約を懸念して、Open RANへの関心が高まっていると考えられる」(Wissolik氏)

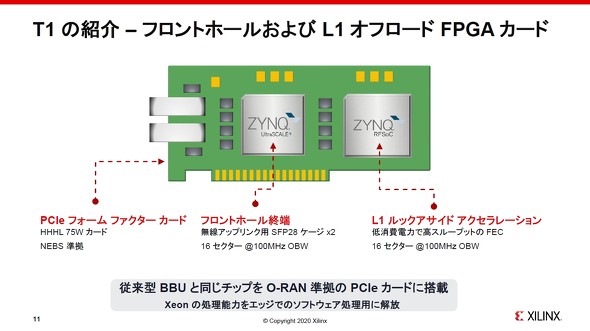

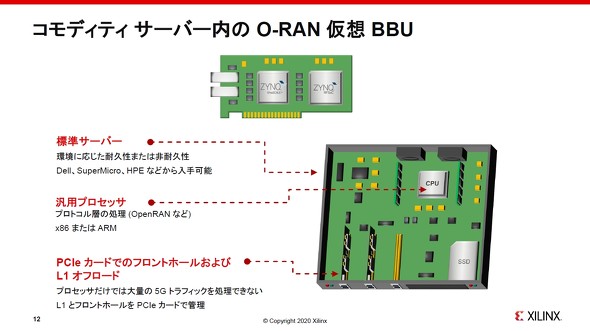

T1は、フロントホールFPGAとL1ベースバンドFPGAをPCI Express(PCIe)フォームファクタカードに搭載。前者にはXilinxの「UltraScale+」を、後者には「RFSoC」を用いており、どちらも5G市場では既に実績があるチップだ。

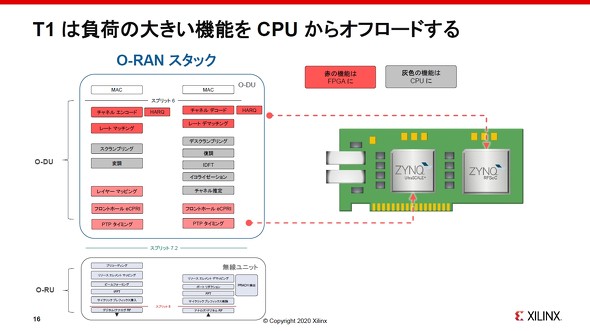

T1は、Open RANに準拠したフロントホール終端と、L1のLDPC-FEC(低密度パリティ検査 前方誤り訂正)に関わる処理を重点的に行うことで、BBU内のCPUの負荷をオフロードする。

Wissolik氏によれば、フロントホール終端とL1のLDPC-FECについては、処理を高速化してほしいという要望が多いという。「特にLDPC-FECは非常に複雑な処理が必要で、従来のBBUに搭載されている汎用CPUでは効率よく処理することが難しい。T1に搭載したRFSoCは、SD-FEC(Soft Decision FEC)と呼ばれる誤り訂正のIP(Intellectual Property)ブロックを内蔵しており、これによってLDPC-FEC関連の演算を高速かつ低消費電力で行える」(同氏)

具体的には、フロントホールFPGAでは、Open RANに準拠したDUの機能において、エンコード、デコード、レートマッチング、データ誤り訂正方式であるHARQ(Hybrid ARQ)などの機能をCPUからオフロードする。一方のL1ベースバンドFPGAでは、レイヤーマッピングやPTPの時刻同期といった機能をCPUからオフロードする。

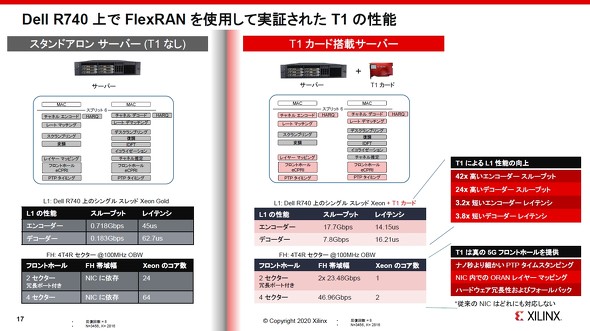

これにより、T1を挿入したサーバと、挿入していないサーバを比較した場合、エンコードスループットは最大45倍、デコードスループットは最大23倍に向上する。「Intelの『FlexRAN』を使用したDellの『PowerEdge R740』サーバで比較した際、エンコードのスループットが0.718Gbpsから17.7Gbpsに、デコードのスループットは0.183Gbpsから7.8Gbpsに向上。レイテンシも、エンコードでは45マイクロ秒から14.15マイクロ秒に、デコードでは62.7マイクロ秒から16.21マイクロ秒と、大幅に短縮された」(Wissolik氏)

つまり、コア数の多いCPUを使う必要がなくなるので、コストと消費電力の大幅な削減につながる。

T1では、拡張性も確保されている。「サーバ1台につきT1カード1枚」ではなく、通信タワーの数が増えた際はT1をサーバに追加すればよい。

XilinxはOpen RANフロントホールおよび5G L1の両方のリファレンスデザインを含めたターンキーソリューションの他、事前検証済みのソフトウェアも用意している。

Wissolik氏は「Open RANは、Xilinxに大きなビジネスチャンスをもたらす市場だ」と語った。

関連記事

5G対応のオープンRANコントローラー、業界団体が開発へ

5G対応のオープンRANコントローラー、業界団体が開発へ

Open Networking Foundation(ONF)は、SD-RAN(Software Defined Radio Access Network)プロジェクトを創設し、モバイル向け4G(第4世代移動通信)および5G(第5世代移動通信) RANの展開に向けてオープンソースのソフトウェアプラットフォームとマルチベンダーソリューションの開発を支援していくことを発表した。 迷走する米中対立、“落とし所なし”の泥沼化

迷走する米中対立、“落とし所なし”の泥沼化

2020年も7カ月が過ぎたが、米中対立は泥沼化している。英調査会社OMDIAのアナリストたちに、米中対立の今と、コロナによるエレクトロニクス業界への影響について語ってもらった。 動画配信を低コストに、Xilinxのビデオアプライアンス

動画配信を低コストに、Xilinxのビデオアプライアンス

Xilinxは2020年6月16日(米国時間)、同社の「リアルタイム(RT)サーバーリファレンスアーキテクチャ」として、ビデオのトランスコーディングに特化したアプライアンス(以下、ビデオアプライアンス)を発表した。同社として初のアプライアンス製品となる。 AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

Xilinxは、組み込み技術の国際展示会「embedded world 2019」(2019年2月26〜28日、ドイツ・ニュルンベルク)で、自動車や監視カメラなどでの推論、いわゆるエッジデバイスでの推論をイメージしたデモを展示した。 パンデミックで通信市場のトレンドにも変化

パンデミックで通信市場のトレンドにも変化

エリクソン・ジャパンは2020年7月13日にオンライン記者説明会を開催し、世界の移動通信市場に関する調査報告書「エリクソンモビリティレポート」の最新版(Ericssonが同年6月16日に発表)について概要を紹介した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

XilinxのMike Wissolik氏

XilinxのMike Wissolik氏