プロセスの最適化を加速する仮想製作プラットフォーム:コストと時間の削減に向けて(1/3 ページ)

高度なCMOSプロセスの微細化やメモリ技術の進化に伴い、デバイス製造における構造がますます複雑化しています。そうした中で、デバイス製造を支援する仮想製作モデリングプラットフォームを紹介します。

高度なCMOSプロセスの微細化やメモリ技術の進化に伴い、デバイス製造における構造がますます複雑化しています。例えば、NAND型フラッシュメモリの場合、垂直方向に拡張するためにメモリスタックの積層数を増やすことによって、面積の微細化を継続しながら、高アスペクト比のエッチングパターンとステアケースにおけるコンタクト層の増加を実現するという課題が生じています。また、微細化の課題を解決するために特別なインテグレーションとパターニングスキームの採用は、デザインルールにおける課題を生み出しています。

2Dのデザインルールチェック(DRC)はもはや、性能と歩留まりの目標を達成するのに十分ではありません。いずれも、工程の特性評価と最適化において実験計画(DOE)にまったく依存していません。従来はレシピ開発のコストと時間を削減するために使用されてきましたが、今やエンジニアは、本工程での膨大な時間とウェハーなどの材料を必要とする、何百ものDOEを用いる必要があります。

さらに、プロセスステップ間の直感的ではない相互作用だけでなく、狭められたプロセスウィンドウも、第一原理モデリングのアプローチを用いた同時実行と歩留まり最適化の実現を難しくしています。複雑なプロセスシーケンスを3Dで理解する必要があります。これはCoventor SEMulator3Dのような仮想製作モデリングプラットフォームによって実現が可能です。

仮想製作モデリングプラットフォームとは

仮想製作モデリングプラットフォームは、一連のユニットプロセスステップから3Dデジタルプロセス統合モデルを作成することによってプロセスフローをエミュレートするソフトウェアです。プロセスシーケンスを完全に統合したモデルを用いる仮想製作モデリングプラットフォームは、プロセス変更による下流での影響を予測することができ、それがなければ工場での構築とテスト(build&test)が必要になります。

例えば、エンジニアはこのソフトウェアを利用して、自己整合ビア(SAV)を採用したトレンチファーストメタルハードマスク(TFMHM)の後工程(BEOL)を用いたリプレースメントメタルゲート(RMG)FinFETを迅速にモデリングできます。3D表示が作成されたことをエンジニアが確認したら、2D/3D計測と電気的特性を抽出できます。

以下、SEMulator3Dを例に挙げて仮想製作モデリングプラットフォームについて紹介します。

このソフトウェアの電気的解析モジュールは、工程と設計感度を把握するために、抵抗およびキャパシタンス抽出を加味します。これは、3Dモデリングと電気的機能の妥当性確認の両方に、単一であるが故に高速なプラットフォームを提供します。SEMulator3Dで使用されているプロセス予測が可能で正確なシリコン構造は、スタンドアロンソルバーで使用される理想的な形状よりも、製作されたデバイスをいっそう正確に反映するため、精度を向上させます。

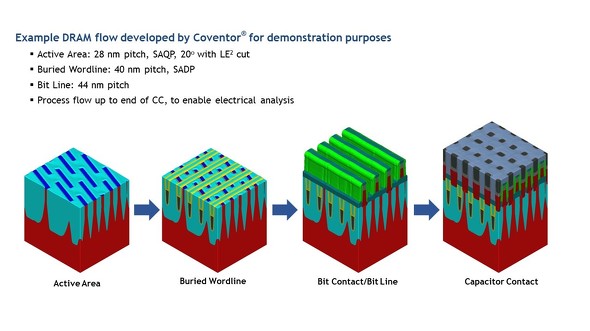

DRAMデモンストレーション

材料選択比やフラックス分布などのエッチング装置機能のばらつきに基づいてプラットフォームがデバイスの電気的性能をモデリングする能力を示すデモンストレーションによって、仮想製作のユースケースが分かりやすく示されます。シンプルなDRAMデバイスのケーススタディでは、事前に目標設定した電気的性能と歩留まりを満たす必要がある、ゲートのエッチング挙動とエッチングステップの特性が強調されています。

このデモンストレーションでは、以下の4つのステップから成る仮想製作の標準的な作業フローを用いています。

- プロセスフローの測定に対応し、デバイス技術の3D予測が可能な構造表示を提供する、工程の名目上の設定

- 構造または電気的動作を限定する目的の指標(計測法、3D DRC、電気的パラメーターなど)の追加

- DOE(実験計画)と測定を伴う設計調査の設定

- 工程の実行や設計の変更に対応する感度解析などのデータ解析

名目上の設定

このデモンストレーションでは、2X DRAMについて名目上の設定を行います。なお、このプロセスフローは、公開されているデータに基づいて実施しています。

このデモンストレーションにおけるDRAMのアクティブ領域(AA)は28nmピッチで、自己整合型クオドルプルパターニング(SAQP)と20度のLELE(Litho-Etch-Litho-Etch)方式を用いています。埋め込みワード線は40nmピッチで自己整合型ダブルパターニング(SADP)を用いており、ビット線は44nmピッチでSADPを用いています。このプロセスフローの終端はキャパシターコンタクト(CC)で、ソフトウェアで電気的解析を行うのに十分であり、キャパシターのエッジ効果を解析する能力があります。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- 東芝との協議やデンソー提案への対応、ロームが新声明

- NVIDIA製GPU搭載サーバのコスト/スペックを分析してみた

- IBMとLamが「サブ1nmチップ」で協業 高NA EUV導入加速へ

- 「これまでにないダイナミックレンジ」 ソニーのLOFIC画素4Kセンサー

- Micron、PSMCの300mm工場買収完了 第2工場も建設へ

- 全固体二次電池の「200℃動作」を実演、日本電気硝子

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- 「世界初」酸化ガリウムをSi基板にエピ成長、名大ら

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方