プロセスの最適化を加速する仮想製作プラットフォーム:コストと時間の削減に向けて(3/3 ページ)

重要なプロセスステップの特定

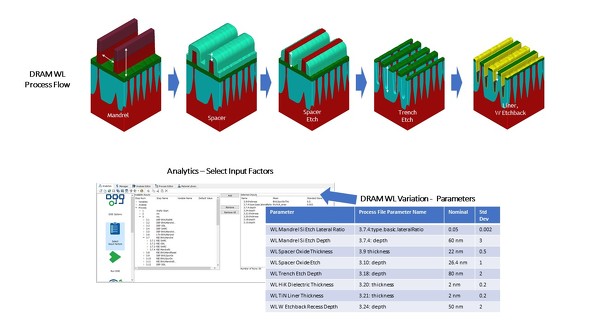

次のステップとして、モンテカルロ法によるばらつきの調査を用いたDOEを実施し、重要なプロセスステップを特定します(図5)。モンテカルロ法を用いたDRAMのワード線(WL)のばらつきは、パラメーターのばらつきの調査に使用されています。

WLプロセスパラメーター値は、平均値または公称値および標準偏差についてガウス分布に基づき無作為に設定されています。このデモンストレーションでは、50回の実験が選択されています。しかしながら、有意義な調査結果を得るには、一般的に100回以上の実験が必要です。

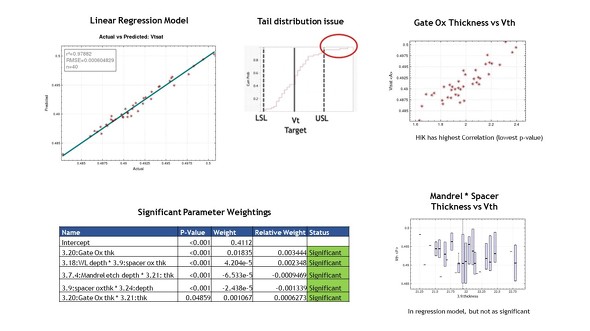

図6はDOEの結果を示しています。DOEでは、閾値電圧(Vt)が0.4837Vから0.5031Vの間でばらついています。SEMulator3Dによる回帰分析は、閾値電圧に及ぼす影響の観点から重要な5つのパラメーターを特定するのに有効です。これらのパラメーターのp値は0.5未満を示しており、帰無仮説を棄却しています。1つ目のパラメーターであるインターセプトは常にリストに記載されるため、今回の説明には含めていません。

さらに詳しい調査で特定された最も重要な5つの要素は以下の通りです。

- ゲート誘電体膜厚(最重要パラメーター)

- 交差するWLのエッチとスペーサ厚さ

- 交差するマンドレルのエッチング深さとゲート厚さ

- 交差するスペーサの酸化膜厚と研磨深さ

- 交差するゲート誘電体膜厚とスペーサ厚さ

直線回帰プロットにおける決定係数(r2)の0.97882という高い値は、モデルがデータに最適であることを意味しています。ゲート誘電体膜厚とVthプロットが強い相関関係を示している一方で、マンドレルのスペーサ厚さとVthプロットはそうした相関関係を示していないため、重要な入力要素の候補から外すことができます。

DOEの結果は、Vthが下限値(LSL)から上限値(USL)までの範囲外であるなど、めったに発生しないケースの特定にも役立つため、エンジニアは詳しく調べた上でプロセス条件を見いだせます。

プロセス最適化

最適化について違った見方をするために、調査の目標として、代わりに電気的特性を使用できます。これにより、電気的な目標を用いることをプロセスステップ最適化の目標にすることができます。プロセスステップの各パラメーターは、電気的性能を満たす条件を探しながら変動させることができます。

使用している装置によって異なるそれぞれのエッチング挙動に対する許容範囲は、ソフトウェアで定義されています。このように、材料エッチング選択性、水平方向の比率、ポリマー/テーパー、スパッタリング、イオンフラックス分布といったパラメーターについてそれぞれの挙動を定義できます。DOEによって特定される重要な入力要素を用いて、電気的性能に対する目標を入力します。

SEMulator3Dは、それらの電気的目標が達成されるように、直接最適化を用いて、WLエッチングに最も適したエッチングステップの挙動プロセスパラメーターを決定します。キャリブレーションされたプロセス案には、酸化膜/シリコン膜/窒化膜の比率、酸化膜および、シリコン膜のテーパー、選択性、側壁角といったパラメーターなどが含まれます。

それらの結果から、プロセス調査において電気的性能が存在していることや、電気性能をその範囲で達成できないことを検証できます。

仮想プロセスによるコストと時間の削減

工程の仮定は、開発初期段階だけでなくハードウェア導入前でも行えるため、実際にウェハーを製作する時間とコストをかけることなく、仮想プロセスでそれらの仮定の妥当性を確認できます。

このDRAMのケーススタディは、仮想環境で数多くのDOEや工程のばらつきの調査を実施することによって、無関係のDOEにかける時間とコストを削減するとともに、性能および、歩留まりの目標を速やかに達成し、市場投入までの時間短縮が可能になることを証明しています。

著

Joseph Ervin/Lam Research 半導体プロセス/統合部門 ディレクター

Lam ResearchのグループであるCoventor社の仮想製作プラットフォームの顧客サポートをするエンジニアのマネジメントに従事。次世代ノードの半導体統合の課題に関して、モデリングなどのユニークな方法を用いた解決方法を展開。アリゾナ州立大学 デバイス物理学 博士号取得。

関連記事

「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

「米国に売られたケンカ」は買うしかない? 絶体絶命のHuaweiに残された手段とは

Huaweiを取り巻く状況が、ますます厳しくなっている。米国による輸出規制の厳格化により、プロセッサだけでなく、CMOSイメージセンサーやメモリ、そしてパネルまでも調達が難しくなる可能性が出てきた。Huaweiが生き残る手段はあるのだろうか。 はんだ印刷位置の精度向上とはんだ量のばらつき低減が課題

はんだ印刷位置の精度向上とはんだ量のばらつき低減が課題

今回から、実装設備に対する具体的な要求項目の重要度(順位)を説明していく。まずは「印刷機(スクリーン印刷機)」を取り上げたい。 EUVスキャナー、出荷は堅調だが稼働率の課題も

EUVスキャナー、出荷は堅調だが稼働率の課題も

SEMI Japanは2020年8月25日、「第6回 SEMI Japanウェビナー」を開催した。今回のウェビナーにはASMLジャパンが登壇し、EUV(極端紫外線)リソグラフィ装置の最新状況を含めた同社の近況を報告した。 無電解めっきを用い高性能有機トランジスタを製造

無電解めっきを用い高性能有機トランジスタを製造

東京大学らの共同研究グループは、「無電解めっき」でパターニングをした金電極を有機半導体に貼り付けた、「高性能有機トランジスタ」の製造に成功した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ロームとデンソー、東芝、三菱電機……国内パワー半導体再編の行方

- AIの競争軸は半導体から電力へ――日本の戦略の「死角」に

- 「NVIDIAとGroqの取引」がAI新興にもたらした2つの効果

- ダイヤモンドMOSFETで初の200V、1AのSW動作を達成

- ローム、デンソーによる買収提案は「事実」

- ロームと東芝、半導体事業の提携強化へ「協議を継続中」

- IntelとSambaNova、提携の行く末――「最もあり得るシナリオ」は?

- 「世界最高」品質の量子光、誤り耐性型量子コンピュータに貢献

- JDI、車載ディスプレイ事業分割を中止「中長期的に最善」

- 目指すは500nm RDL 太陽HDがimecと挑む次世代パッケージング材料