異種デバイスの融合を実現する3次元集積化技術:福田昭のデバイス通信(296) Intelが語るオンチップの多層配線技術(17)(1/2 ページ)

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。

シングルダイよりも低いコストで複数の機能を搭載

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。その中で「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」を共通テーマとする講演、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」が非常に興味深かった。そこで講演の概要を本コラムの第280回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの前々回と前回は、「自己組織化単分子(SAM:Self-Assembled Monolayer)膜」による選択成長技術がビアの位置ずれ不良を救済できることと、選択成長の工程をご報告した。

今回は、異種デバイスの融合を実現する3次元(3D)集積化技術の概要を説明する。異なるプロセス技術で製造したシリコンウエハーあるいはシリコンダイを積層することで、1個のパッケージに複数の機能を収容する。1枚のシリコンダイ(シングルダイ)にプロセスの異なる複数の機能を集積することに比べ、低いコストで数多くの機能を実装できる。

はんだのマイクロバンプで25μmと短いピッチを接続

3次元積層で重要なのは、シリコンを積層するときの接続技術だ。単位面積当たりのデータ転送を高めるためには、高い密度で異なるシリコンを接続する必要がある。基本的な考え方としては、シリコン表面(あるいは基板表面)に対して垂直な方向で2次元アレイ状に接続電極をレイアウトする。

2次元アレイ状の接続技術で最も普及しているのは、はんだバンプを使った接続(はんだ接合)だろう。マイクロバンプと呼ばれる微小なはんだバンプによってシリコンウエハーやシリコンダイ、樹脂基板などを高い密度で接続する。接続ピッチはバンプの大きさによって決まる。最短で25μm〜30μmくらいだ。

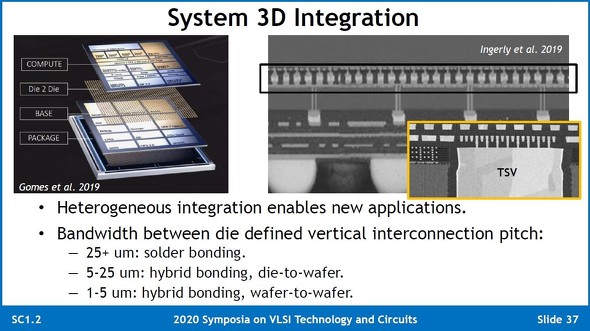

3次元集積化(3D Integration)による異種デバイスの融合(Heterogeneous Integration)。2次元アレイ状にレイアウトした接続電極のピッチが接続密度を決める。単位面積当たりのデータ転送速度を高めるためには、高い密度の接続、言い換えると短いピッチの接続が望まれる。はんだ接合(マイクロバンプ接合)では25μm強まで、ハイブリッド接合では25μm以下のピッチを狙える。出典:Intel(クリックで拡大)

3次元集積化(3D Integration)による異種デバイスの融合(Heterogeneous Integration)。2次元アレイ状にレイアウトした接続電極のピッチが接続密度を決める。単位面積当たりのデータ転送速度を高めるためには、高い密度の接続、言い換えると短いピッチの接続が望まれる。はんだ接合(マイクロバンプ接合)では25μm強まで、ハイブリッド接合では25μm以下のピッチを狙える。出典:Intel(クリックで拡大)さらに短い接続ピッチでは、はんだ接合は適用が難しい。シリコンウエハーやシリコンダイなどの表面に形成した銅(Cu)電極同士を貼り合わせて接続する「ハイブリッド接合(Hybrid Bonding)」が使われる。ハイブリッド接合技術だと、シリコンウエハーとシリコンダイの接続では25μm〜5μm、シリコンウエハー同士の接続では5μm〜1μmと極めて短いピッチを狙える。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長