IBM、8ビット学習が可能なテストチップを発表:「ISSCC 2021」(1/2 ページ)

IBM Researchは、2021年2月13〜22日にオンライン開催された半導体業界最大級の国際学会「ISSCC 2021」において、テストチップを発表した。これは、同社が長年にわたり取り組んできた、低精度のAI(人工知能、ここでは機械学習)トレーニング/推論アルゴリズムを具現化したハードウェアだといえる。

低精度での学習/推論が可能に

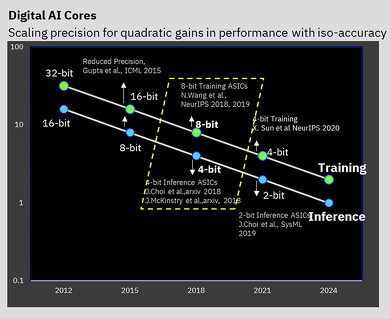

IBM Researchは、2021年2月13〜22日にオンライン開催された半導体業界最大級の国際学会「ISSCC 2021」において、テストチップを発表した。これは、同社が長年にわたり取り組んできた、低精度のAI(人工知能、ここでは機械学習)トレーニング/推論アルゴリズムを具現化したハードウェアだといえる。4コアを搭載し、7nmプロセスを適用したこのチップは、16ビットおよび8ビットのトレーニングだけでなく、4ビットおよび2ビットの推論もサポート可能だという(業界では現在、32ビットまたは16ビットのトレーニングと、8ビット推論が標準とされている)。

精度を低下させると、AI計算に必要とされる計算量や性能が大幅に低下する可能性があるが、IBMは、効率向上を実現することが可能なアーキテクチャ関連の秘策をいくつか用意しているという。そこで課題となるのが、計算結果にマイナスの影響を及ぼすことなく精度を低下させるという点だ。これは、IBMがこれまで長年にわたり、アルゴリズムレベルで進めてきた取り組みの1つである。

IBMは、2019年にAIハードウェアセンターを設立し、AI計算性能を毎年2.5倍に向上させることを目指してきた。最終的には2029年までに、電力性能比(FLOPS/W)を1000倍に高めるという野心的な目標を掲げている。

このような目標が必要とされた背景には、AIモデルのサイズや、そのトレーニングに必要な計算量が急激に拡大しているということがある。特に、自然言語処理(NLP)モデルは今や、1兆個規模の巨大なパラメータを持ち、その膨大な量のトレーニングに伴って排出される二酸化炭素排出量についても、見過ごすことはできない。

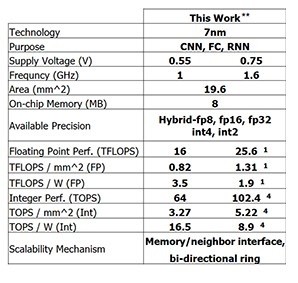

今回IBM Researchが発表したテストチップは、IBMがこれまでに実現してきた成果を示す存在だといえる。8ビットトレーニングに関しては25.6TFLOPSを実現し、4ビットの整数計算では102.4TOPSの推論性能を達成することが可能だ(クロック周波数が1.6GHz、供給電圧が0.75Vの場合)。クロック周波数を1GHz、供給電圧を0.55Vにそれぞれ下げると、電力効率を3.5TFLOPS/W(FP8)または16.5TOPS/W(INT4)に高められるという。

このような性能は、IBMが長年にわたり行ってきた、低精度トレーニングおよび推論技術に関するアルゴリズムの取り組みをベースとしている。IBM独自の8ビットハイブリッド浮動小数点フォーマット(Hybrid FP8)を初めてサポートすることが可能なチップである。Hybrid FP8は、機械学習分野の最高峰の国際会議である「NeurIPS(Neural Information Processing Systems) 2019」において初めて発表された。この新しいフォーマットは、特に8ビットトレーニングを可能にすることを目的として開発され、16ビットトレーニングに必要な計算性能を、マイナスの影響を与えることなく半減することが可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

IBM Researchが発表したテストチップの概要および性能 出典:IBM Research

IBM Researchが発表したテストチップの概要および性能 出典:IBM Research