3D NANDフラッシュの製造歩留まりを高める2段階積層:福田昭のストレージ通信(190) アナリストが語る不揮発性メモリの最新動向(17)(1/2 ページ)

今回は、3D NANDフラッシュの製造工程の中で最も困難とされる、「メモリスルーホール」の形成プロセスに関する講演部分をご報告する。

製造が最も困難なメモリスルーホール形成

フラッシュメモリとその応用に関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」が2020年11月10日〜12日に開催された。FMSは2019年まで、毎年8月上旬あるいは8月中旬に米国カリフォルニア州サンタクララで実施されてきた。COVID-19(新型コロナウイルス感染症)の世界的な大流行(パンデミック)による影響で、2020年のFMS(FMS 2020)は開催時期が3カ月ほど延期されるとともに、バーチャルイベントとして開催された。

FMSは数多くの講演と、展示会で構成される。その中で、フラッシュメモリを含めた不揮発性メモリとストレージの動向に関するセッション「C-9: Flash Technology Advances Lead to New Storage Capabilities」が興味深かった。このセッションは4件の講演があり、その中でアナリストによる3件の講演が特に参考になったので、講演の概要をご紹介する。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの第10回から、技術調査会社TechInsightsでシニア技術フェローをつとめるJeodong Choe氏が「Technology Trend:NAND & Emerging Memory(NANDフラッシュメモリと次世代メモリの技術動向)」と題して講演した内容を説明している。前々回(第15回)は中国のYMTCが開発した3D NANDフラッシュメモリ(以降は「3D NANDフラッシュ」と表記)技術と応用製品を、前回(第16回)はSK hynixが製造技術で最後発からトップグループに追い付くまでの経緯を簡単に解説した。

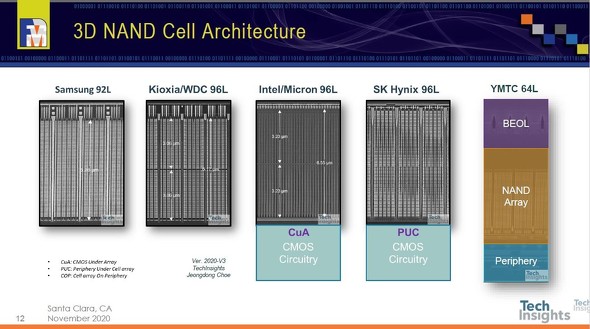

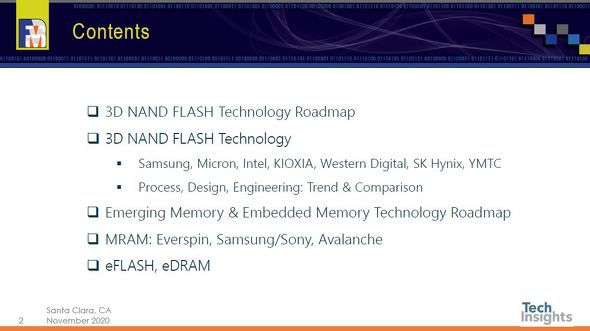

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

講演のアウトライン。3D NANDフラッシュの開発ロードマップと要素技術、次世代メモリと埋め込みメモリの開発ロードマップなどを解説する。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)今回は、3D NANDフラッシュの製造工程の中で最も困難とされる、「メモリスルーホール」の形成プロセスに関する講演部分をご報告する。「メモリスルーホール」とは、導電膜層(ワード線や共通ゲート線など)と絶縁膜層を交互に成膜した後で、全体を垂直に貫通する孔(ホール)を指す。この孔に多結晶シリコンを埋め込むことで、セルトランジスタのチャンネルを形成する。

ワード線積層とスルーホール形成を2つのステップに分ける

「メモリスルーホール」の製造は極めて難しい。細くて深い孔(メモリスルーホール)を膨大な数で均一に形成することが要求されるからだ。しかもワード線の積層数が増えるとともに、製造の難しさが高くなり、製造歩留まりが低下する恐れが強まる。

メモリスルーホール製造の難しさを緩和する有力な手法が、メモリスタック(セルストリング)の製造を2段階に分けることだ。例えばワード線の積層数が64層のときは、まず32層分のメモリスタック(セルストリング)を作る。その上に、残り32層分のメモリスタックを形成する。全体では64層のメモリスタックを、32層分のメモリスルーホール形成と同様の難度で作れる。

分割されたメモリスタック(Memory Stack)は、「ティアー(Tier)」あるいは「デッキ(Deck)」と呼ぶことが少なくない。単に「スタック」と呼ぶこともある。下側のスタックは「ローワースタック(Lower Stack)」「ローワーデッキ」、上側のスタックは「アッパースタック(Upper Stack)」「アッパーデッキ」などと名付けて区別する。

TechInsightsのChoe氏は講演で、ワード線の積層数が92層〜96層の3D NANDフラッシュを作り込んだシリコンダイを切断してメモリセルアレイの断面を電子顕微鏡で観察した画像を示していた。Samsung Electronics(以降は「Samsung」と表記)は92層でメモリスタックは1個だけ。1回のメモリスルーホール形成で全スタックを貫通させているのは同社だけだ。キオクシア-Western Digital(以降は「WD」と表記)連合、Intel-Micron Technology(以降は「Micron」と表記)連合、SK hynixはメモリスルーホールの形成を2段階に分けている。すなわちローワーデッキとアッパーデッキがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増