3D NANDフラッシュの製造歩留まりを高める2段階積層:福田昭のストレージ通信(190) アナリストが語る不揮発性メモリの最新動向(17)(2/2 ページ)

2ティアー(2デッキ)構造は位置合わせと接続部が課題

メモリスルーホール形成(セルストリング形成)を2段階に分ける手法には当然、いくつかの課題が存在する。まず、上側のスタックと下側のスタックの位置を正確に合わせなければならない。また上下のスタックを接続する部分の構造をどのようにするかも課題となる。さらに、1回のスルーホール形成で全スタックを構築するプロセスに比べると生産のスループットは低下する。

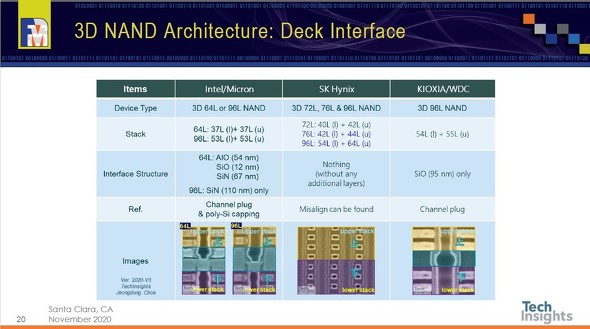

講演では、Intel-Micron連合、SK hynix、キオクシア-WD連合の3D NANDフラッシュを分析して2つのデッキの構成と接続部を電子顕微鏡で観察した結果を述べていた。Intel-Micron連合の3D NANDフラッシュではワード線の積層数で64層の世代と96層の世代を分析した。

64層世代のスタック(デッキ)は下側が37層、上側が37層である。合計が64層よりも多いのは、ワード線以外の導電層(共通ゲート層やダミーワード線など)が存在するためだ。96層世代のスタック(デッキ)は下側が53層、上側が53層である。上下のデッキを接続する部分は、チャンネルのプラグおよびキャップと、絶縁層で構成する。

SK hynixの3D NANDフラッシュではワード線の積層数で72/76層の世代と96層の世代を分析した。72/76層世代のスタック(デッキ)は下側が40/42層、上側が42/44層である。96層世代のスタック(デッキ)は下側が54層、上側が64層である。いずれも上側のデッキの層数が多い。上下のデッキを接続する部分は特に設けず、下側と上側のデッキを直結している。

キオクシア-WD連合の3D NANDフラッシュではワード線の積層数で96層の世代を分析した。デッキは下側が54層、上側が55層である。上下のデッキを接続する部分は、チャンネルのプラグと酸化膜で構成する。

2ティアー(あるいは2デッキ)構造を採用したメモリスタックの接続部。左からIntel-Micron連合、SK hynix、キオクシア-WD連合。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)

2ティアー(あるいは2デッキ)構造を採用したメモリスタックの接続部。左からIntel-Micron連合、SK hynix、キオクシア-WD連合。出典:FMS 2020の講演「Technology Trend:NAND & Emerging Memory」の配布資料(クリックで拡大)(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

中国の3D NANDフラッシュメーカー「YMTC」の現状

中国の3D NANDフラッシュメーカー「YMTC」の現状

今回は、中国の3D NANDフラッシュベンチャーであるYMTC(Yangtze Memory Technologies Co., Ltd.)の現状に関する講演部分を紹介する。 高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

高層化の継続で、製造コストを爆下げする3D NANDフラッシュ

今回からは、半導体メモリのアナリストであるMark Webb氏の「Flash Memory Technologies and Costs Through 2025(フラッシュメモリの技術とコストを2025年まで展望する)」と題する講演の概要をご紹介する。 ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーが20年度通期業績を上方修正、CMOSセンサーも想定上回る

ソニーは2021年2月3日、2021年3月期(2020年度)第3四半期(2020年10〜12月期)決算を発表するとともに、2020年度通期業績予想を上方修正した。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- デンソー、ロームに対する株式取得提案を正式表明

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- ソニー・ホンダモビリティ、EV「AFEELA」開発中止

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響