IBMが「2nm」プロセスのナノシートトランジスタを公開:GAAアーキテクチャを採用(1/2 ページ)

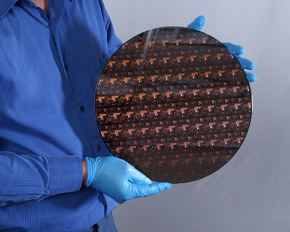

IBMは、米国ニューヨーク州アルバニーにある研究開発施設で製造した「世界初」(同社)となる2nmプロセスを適用したチップを発表した。同チップは、IBMのナノシート技術で構築したGAA(Gate-All-Around)トランジスタを搭載している。

GAAトランジスタを搭載

IBMは、米国ニューヨーク州アルバニーにある研究開発施設で製造した「世界初」(同社)となる2nmプロセスを適用したチップを発表した。同チップは、IBMのナノシート技術で構築したGAA(Gate-All-Around)トランジスタを搭載している。同社は、「この新しいプロセス技術によって、2nmチップは、現在生産している最先端の7nmチップと比べて45%の性能向上と75%の消費電力削減を実現できる」と述べている。

IBMは、7nmと5nmのテストチップのデモンストレーションも業界で初めて行っている。IBMが発表したテストチップは、約500億個のトランジスタを搭載し、GAAトランジスタの一部にナノシート構造を採用している。GAAは、その前身となるFinFETのスケーリングの限界に対する解決策として開発された新しいトランジスタアーキテクチャである。

FinFETは、Intelが22nmノード向けに2011年に商用化した。GAAトランジスタは、FinFETのフィンを3本のワイヤに置き換え、ゲート材料で四方を囲んでいる。このようにチャネル材料を囲むことで、静電制御が向上し、ゲート寸法を非常に小さくすることができる。

ナノワイヤでは、ワイヤをエピタキシャル成長させることで、チャネルの厚さ(ワイヤの厚さ)を慎重に制御できる。FinFETは、作成にリソグラフィと反応性イオンエッチングプロセスを使用するため、チャネルの厚さを厳密に制御することができない。

最初のGAAトランジスタは、単一のナノワイヤを使用していたため、寸法が小さくリーク電流は少ないが、電流が制限されるためスイッチングが遅かった。これに対し、同様にGAA技術を適用しているSamsung Electronicsの「Multibridge Channel FET」は、チャネルにより多くの電流が流れるように複数のワイヤを垂直に積層している。

ワイヤをナノシートに展開すると、リーク電流を厳密に制御しながらチャネル幅を広げることができる。ナノシートは幅を変えて構築することもできるため、FinFETにはなかった平面トランジスタの柔軟性を実現できる。さらに、ナノシートの幅を広げてより多くの電流を流したり、狭めて消費電力を抑えたりすることもできる。

ナノシートベースのプロセスは、TSMCなどのファウンドリーが3nmノード向けに準備を進めている。

IBMの2nmチップでは、各トランジスタは幅40nm、高さ5nmのナノシートを3枚積層する(参考までに、5nmは2本のDNA鎖とほぼ同じ厚さである)。トランジスタのピッチは44nmで、ゲート長は12nmである。

なお、「2nm」という名称は、チップのフィーチャサイズとは何の関係もない。プロセスノードの名称は、そのフィーチャサイズのプレーナー型トランジスタと同等の性能を反映させることを意図している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増