IBMが「2nm」プロセスのナノシートトランジスタを公開:GAAアーキテクチャを採用(2/2 ページ)

2nmチップに適用した主要技術

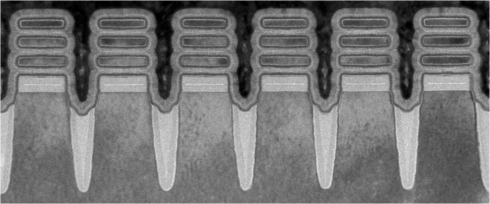

IBMは、ナノシートトランジスタの小型化を実現した複数の主要技術の内容を明らかにした。まずは、底部の絶縁層分離を利用した技術で、ナノシートとバルクウエハーの間のリーク電流を除去することが可能だという。リーク電流を低減する必要があるのは、ゲート長を12nmまで縮小するためだ。

またエッチングでは、インナースペース形成で第2世代のドライプロセスを適用することにより、ゲートのサイズを正確に制御することが可能になった。同ドライプロセスは、IBMの等方性エッチング技術をベースとしている。さらに、新しいマルチスレッショルド電圧手法により、モバイルからハイエンドサーバ向けチップまで、幅広いアプリケーションに対してスレッショルド電圧制御を行うことが可能だという。

ここで重要なのが、今回のチップが、業界で初めてFEOL(Front End of Line)にEUV(極端紫外線)リソグラフィを適用したという点である。EUVは既に、MEOL(Middle End of Line)やBEOL(Back End of Line)などで使われているが、ナノシートやゲートなどの重要な機能に適用されたのは、今回の2nmチップが初めてとなる。この技術により、シート幅を15〜70nmの間で変化させることが可能になった。

新しい2nmプロセス技術は実質的に、モバイルやハイエンドサーバ、HPC(ハイパフォーマンスコンピューティング)など、あらゆる種類のアプリケーションに適用されるようになるだろう。例えば、AI(人工知能)や、5G/6G(第5/第6世代移動通信)、自律システム、量子コンピューティングなどが挙げられる。もちろんIBMの高性能サーバ「IBM Power Systems」や「IBM Z」プラットフォームなどにも適用される見込みだが、デバイスの製造に関しては、引き続きIBMの製造パートナーであるSamsung Electronicsに委託するようだ。

今回2nmチップを実現するに至った技術開発は、IBMと、IBM Research Ecosystemのパートナー各社が、長年にわたって取り組みを進めてきた成果だといえる。その中の1社であるIntelは、自社のファウンドリー事業を強化して進めてきいく予定であることを発表し、最近エコシステムに参加したばかりだ。IBMは、Intelが将来的に、この技術を自社の2nmプロセスに適用するかどうかについては明らかにしていないが、その可能性は高いと思われる。

今回のテストチップを実現した技術が、製造において実用化されるまでには、歩留まりの向上やデバイス設計関連の取り組みをはじめ、膨大な作業を行う必要がある。IBMは、こうした取り組みをベースとして、2024年末には2nmプロセスのファウンドリー技術を適用した生産に入る予定だとしている。

【翻訳:滝本麻貴、田中留美、編集:EE Times Japan】

関連記事

IBM、8ビット学習が可能なテストチップを発表

IBM、8ビット学習が可能なテストチップを発表

IBM Researchは、2021年2月13〜22日にオンライン開催された半導体業界最大級の国際学会「ISSCC 2021」において、テストチップを発表した。これは、同社が長年にわたり取り組んできた、低精度のAI(人工知能、ここでは機械学習)トレーニング/推論アルゴリズムを具現化したハードウェアだといえる。 米半導体企業、大統領に支援を求める書簡を送付

米半導体企業、大統領に支援を求める書簡を送付

主要な半導体企業のCEOが米国バイデン大統領に対して半導体製造/研究に対する財政的支援を優先するよう強く求める書簡に署名したことを受け、ホワイトハウス報道官のJen Psaki氏は、2021年2月8日の週に行われた記者会見の中で、半導体業界は数週間以内に大統領命令への署名を見込めるはずだと述べた。 富士通、量子コンピュータ実現に向け研究を本格化

富士通、量子コンピュータ実現に向け研究を本格化

富士通は2020年10月13日、オンラインで研究開発戦略説明会を実施。量子コンピュータの実現に向け、理化学研究所(理研)や東京大学、大阪大学、オランダのデルフト工科大学の4研究機関と共同研究を開始することを明かした。富士通研究所ICTシステム研究所量子コンピューティングプロジェクトのプロジェクトディレクター、佐藤信太郎氏は、「先の長い研究だが、この分野で共同研究先とともに世界をリードし、将来的に社会課題解決に貢献したい」と語った。 IBM、量子ボリュームで自社最高の「64」を達成

IBM、量子ボリュームで自社最高の「64」を達成

IBMは、量子コンピュータの性能を表す「量子ボリューム」という指標で「64」を達成した。自社製品では最高値となる。 TSMCが2021年の設備投資を300億ドルに再度引き上げ

TSMCが2021年の設備投資を300億ドルに再度引き上げ

世界最大の半導体ファウンドリーであるTSMCは、顧客需要が3カ月前の同社の予想を上回ったことを受け、2021年の設備投資額を再度引き上げて、300億米ドルに増額した。 TSMCとSamsungのEUV争奪戦の行方 〜“逆転劇”はあり得るか?

TSMCとSamsungのEUV争奪戦の行方 〜“逆転劇”はあり得るか?

2020年、ASMLのEUV(極端紫外線)露光装置は大ブレークした。この最先端装置をめぐり、争奪戦を繰り広げているのがTSMCとSamsung Electronicsだ。2社の争奪戦の行方について考察した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増