TSMCの最新プロセスまとめ、3nm以降の開発も進行中:2021 Technology Symposium

TSMCは2021年6月1〜2日に、自社イベント「2021 Technology Symposium」をオンラインで開催した。同イベントで発表された最新プロセスノードなどをまとめる。

TSMCは2021年6月1〜2日に、自社イベント「2021 Technology Symposium」をオンラインで開催した。同イベントで発表された最新プロセスノードなどをまとめる。

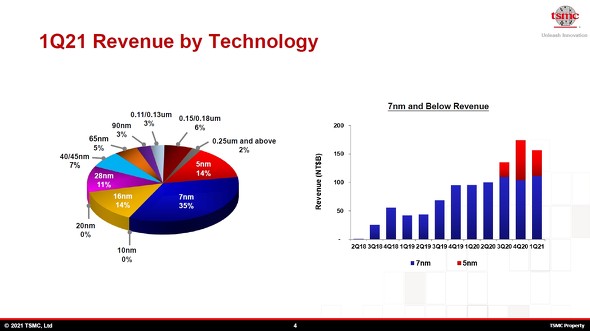

まずはスマートフォンやHPC(High Performance Computing)に使われる最先端プロセスノードだ。2020年にいち早く量産を開始した5nmプロセス「N5」は、TSMCの2021年第1四半期の売上高(129億2000万米ドル)において、既に14%を占めるようになっている。プロセス別に見ると7nmが35%、16nmが14%、28nmが11%となっている。

N5に加え、2020年のTechnology Symposiumでは「N4」の存在を明らかにしている。N4は、N5ファミリーの一つであり、N5に比べてマスク層数は減らしつつ、性能と電力効率、トランジスタ密度を向上している。TSMCはN4の開発は順調に進んでいると述べていて、2021年第3四半期にリスク生産が始まる予定で、量産出荷は2022年になる計画だ。

N5の最新ファミリーとして発表されたのが「N5A」だ。機械学習を使うドライバーアシスタント機能やクルマのコックピットのデジタル化など、主に車載アプリケーションに必要とされる高い性能を提供するためのプロセスだ。「自動車の“HPC化”が進む、TSMC」にも書かれている通り、TSMCのAutomotive Service Packageを搭載した「N7」に比べ、N5Aの性能は最大20%、電力効率は最大40%、ロジック密度は最大80%向上するという。車載規格であるAEC-Q100 Grade 2に準拠するチップを製造できるとする。N5Aは、2022年第3四半期に量産が始まる予定だ。

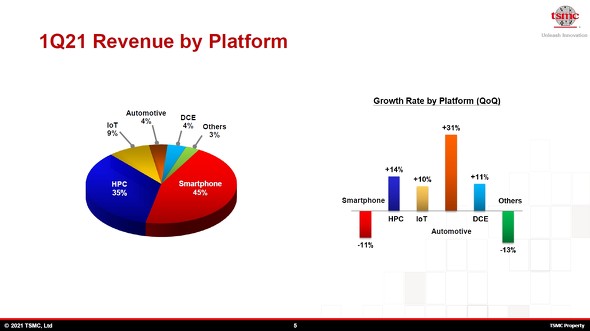

TSMCの2021年第1四半期の分野別の売上高。オートモーティブは4%と非常に少ないが、図版右側に示されている通り、前四半期比では31%増と最も伸びており、今後も大きく伸びる可能性がある 出典:TSMC(クリックで拡大)

TSMCの2021年第1四半期の分野別の売上高。オートモーティブは4%と非常に少ないが、図版右側に示されている通り、前四半期比では31%増と最も伸びており、今後も大きく伸びる可能性がある 出典:TSMC(クリックで拡大)最先端となる「N3」については、2022年後半に量産を開始する。FinFETを活用し、N5に比べて消費電力が最大30%減となり、15%高速化し、ロジック密度は最大70%向上するという。なお、3nmの開発/製造拠点は、5nm同様、「Fab 18」となる。

5G(第5世代移動通信)やWi-Fi 6/6Eに向けては、6nmプロセスの「N6RF」を発表した。前世代の16nmプロセスを適用したRFチップに比べて、性能が16%以上向上する。さらに、サブ6GHz帯をサポートするRFチップとミリ波帯をサポートするRFチップにおいて、消費電力とチップ面積を大幅に低減できるという。

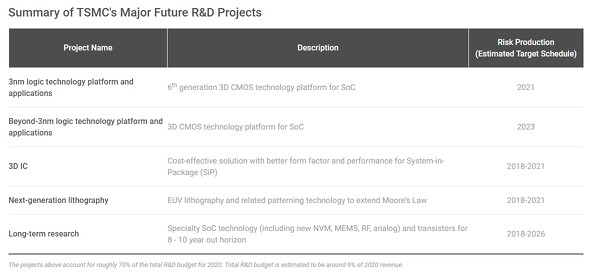

TSMCは今後のR&D計画についても、同社のWebサイトで公開している。3nm以降のロジック技術(3D CMOS技術)については、2023年のリスク生産を目指して開発を進めているさなかだ。

関連記事

CMOSロジックの高密度化を後押しする次世代の電源配線技術

CMOSロジックの高密度化を後押しする次世代の電源配線技術

今回は、CMOSロジックの高密度化手法を簡単に解説する。 半導体不足は「ジャストインタイム」が生んだ弊害、TSMCが急所を握る自動運転車

半導体不足は「ジャストインタイム」が生んだ弊害、TSMCが急所を握る自動運転車

深刻な半導体不足が続く中、自動車メーカーは苦境に陥っている。だが、この苦境は自動車メーカー自らが生み出したものではないか。特に筆者は、「ジャストインタイム」生産方式が諸悪の根源だと考えている。 TSMCが90億ドルの資金調達へ、日本に子会社設立も

TSMCが90億ドルの資金調達へ、日本に子会社設立も

TSMCは、生産を拡大すべく、2種類の債権売却によって約90億米ドルの資金を調達する予定であると発表した。深刻な半導体チップ不足を解消していきたい考えだという。 半導体不足という「有事」が問うニッポン半導体産業のあるべき姿

半導体不足という「有事」が問うニッポン半導体産業のあるべき姿

2021年2月6日付の日本経済新聞1面に「半導体『持たざる経営』転機 有事の供給にリスク」という記事が掲載された。昨今はこの記事以外にも半導体業界に関する記事が注目を集めているようで、この業界に長らく関わっている筆者としてもありがたいことだ。ただ、半導体業界関連の記事をよく読んでみると「そうかな?」と首をかしげる記事も少なくない。冒頭に挙げた記事も、分かりやすく簡潔にまとまっているように見えるが、逆にまとまり過ぎていて、筆者の主張したいことが多々こぼれ落ちているように読めた。そこで、今回は半導体産業のあるべき姿について、私見を述べさせていただくことにする。 NXP、車載プロセッサをTSMCの16nm技術で量産

NXP、車載プロセッサをTSMCの16nm技術で量産

NXP Semiconductorsは、車載ネットワークプロセッサ「S32G2」とレーダープロセッサ「S32R294」について、TSMCの16nm FinFETプロセス技術を用いて、2021年第2四半期(4〜6月)より量産を始めた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 全固体電池の製造プロセス簡素化、東北大が新手法

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める