Intelがプロセスの名称を変更、「nm」から脱却へ:パッケージング技術の最新情報も(1/2 ページ)

Intelは2021年7月26日(米国時間)、半導体プロセスとパッケージング技術の最新情報を説明するウェブキャスト「Intel Accelerated」を開催した。これを受けて、同社の日本法人インテルは7月28日に、Intel Acceleratedの内容を日本のメディア向けに説明するオンライン説明会を実施。インテル 執行役員常務 技術本部本部長である土岐 英秋氏が説明した。

Intelは2021年7月26日(米国時間)、半導体プロセスとパッケージング技術の最新情報を説明するウェブキャスト「Intel Accelerated」を開催した。これを受けて、同社の日本法人インテルは7月28日に、Intel Acceleratedの内容を日本のメディア向けに説明するオンライン説明会を実施。インテル 執行役員常務 技術本部本部長である土岐英秋氏が説明した。

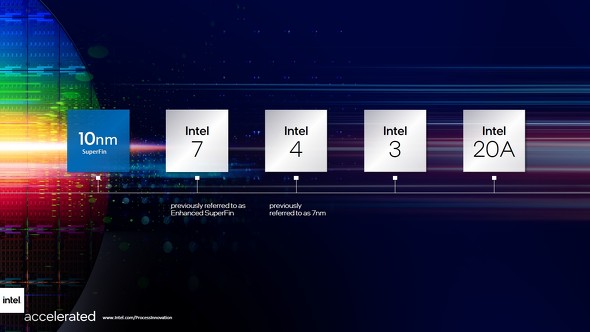

半導体プロセスで最も重要なアップデートは、プロセスノードの名称の変更である。これまで「22nm」「14nm」といったように「ナノメートル(nm)」を使って世代を表していたが、10nm世代の改良版である「10nm SuperFin」の次の世代からこれを一新し、「Intel 7」「Intel 4」「Intel 3」「Intel 20A」とする名称に変更する。このうち、Intel 7はIntelがこれまで「10nm Enhanced SuperFin」と呼んでいたもの、Intel 3はいわゆる7nm世代としていたものを指す。

さらに、Intel 4からはEUV(極端紫外線)リソグラフィー技術を導入。Intel 20Aからは、新しいトランジスタ構造として「RibbonFET(リボンFET)」と「PowerVia(パワービア)」を導入する予定だ。

左=「Intel 7」は、「10nm SuperFin」に比べて、1W当たりのトランジスタ性能が10〜15%向上するという/右=「Intel 3」では、EUVの強化が行われ、「Intel 4」に比べて1W当たりのトランジスタ性能が約18%向上するとしている 出典:Intel(クリックで拡大)

左=「Intel 7」は、「10nm SuperFin」に比べて、1W当たりのトランジスタ性能が10〜15%向上するという/右=「Intel 3」では、EUVの強化が行われ、「Intel 4」に比べて1W当たりのトランジスタ性能が約18%向上するとしている 出典:Intel(クリックで拡大)それぞれの世代の導入時期と量産開始時期、トランジスタの構造、どのプロセッサに適用されるのかを、以下にまとめる。

| プロセスノード | Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A |

|---|---|---|---|---|---|

| 製造開始 | 2021年 | 2022年後半 | 2023年後半 | 2024年 | 2025年前半 |

| 出荷開始 | 2022年 | 2023年 | 2024年 | ||

| 適用されるチップ | 「Alder Lake」 「Sapphire Rapids」 |

「Meteor Lake」 「Granite Rapids」 |

|||

| トランジスタ構造 | FinFET | FinFET | FinFET | RibbonFET | RibbonFET |

| 導入する技術 | EUVリソグラフィ | PowerVia | |||

名称を変更した理由について土岐氏は、「Intelがファウンドリー事業『IFS(Intel Foundry Services)』を始めるにあたり、どのトランジスタノードがどの世代なのかをより分かりやすくするためだ」と説明した。

半導体製造技術のプロセスノードは、プレーナ型FETでは、基本的にはゲートの長さを表していた。だが、FinFETが登場してからは、その構造上の都合から、プロセスノードが“どこの長さ”を示すのかが曖昧になり、半導体メーカー/ファウンドリー各社がいうところの「XXnm」は、世代を表す数字としては機能しているものの、物理的な長さを表す数字としてはほとんど意味を持たず、ブランド名やモデル名といったイメージに近いものとなっていた。

Intel 20Aに関しても同じことがいえる。この「A」はオングストローム(10−10m/0.1nm)を指しているが、Intel 20Aは、トランジスタのどこかのサイズが20オングストロームだと言いたいわけではない。「当社はかつて、ゲート酸化膜の厚さが原子何個分(にまで薄くなる)、ということを紹介したことがある。Intel 20Aは、微細加工が進み、トランジスタが、原子が見えるレベルにまで小さくなってきたことを示すもので、いよいよトランジスタも“オングストローム世代”(=オングストロームでカウントできる部分があるということ)に入ってきたことを表している」(土岐氏)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング