EE Times Japan >

LSI >

多層配線のビア抵抗を大幅に低減する「スーパービア」:福田昭のデバイス通信(322) imecが語る3nm以降のCMOS技術(25)(2/2 ページ)

» 2021年09月16日 11時30分 公開

[福田昭,EE Times Japan]

2層分の配線間を一気に貫通する「スーパービア」

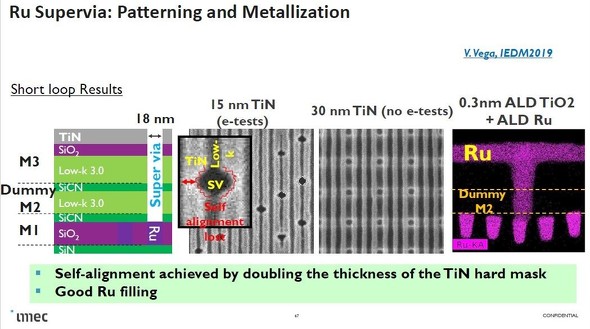

そこで考案されたのが、M3からM1を一気に貫通するビア「スーパービア(supervia)」である。製造工程は、例えば以下のようになる。M1とM2(あるいはダミーのM2)を形成し、M2の上に層間絶縁膜を成膜する。その上に窒化チタン(TiN)のハードマスクを堆積し、M1の表面まで貫通する垂直な孔(スーパービア)を掘る。それからスーパービアに高融点金属(例えばルテニウム(Ru))を埋め込むとともに、M3を成膜する。

第3層金属配線(M3)と第1層金属配線(M1)を接続するスーパービアの製造工程。左端は構造図。M2はダミー層である。右端はM3を形成後の断面を、エネルギー分散型X線分光分析装置(EDS装置)と電子顕微鏡で観察した画像。中央の写真2点はハードマスク(TiN)層の厚みによるビアパターンの違い。TiN層を30nmと厚くすることで、良好なパターンを得られる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

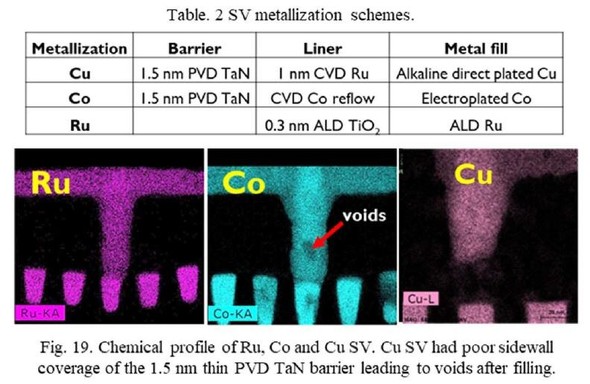

第3層金属配線(M3)と第1層金属配線(M1)を接続するスーパービアの製造工程。左端は構造図。M2はダミー層である。右端はM3を形成後の断面を、エネルギー分散型X線分光分析装置(EDS装置)と電子顕微鏡で観察した画像。中央の写真2点はハードマスク(TiN)層の厚みによるビアパターンの違い。TiN層を30nmと厚くすることで、良好なパターンを得られる。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)imecは、銅(Cu)とコバルト(Co)、ルテニウム(Ru)でそれぞれ、M1とM3を接続するスーパービアを試作してみた。銅(Cu)はビア底部内壁への埋め込みが不十分であり、コバルト(Co)はビア電極内部にボイド(空孔)が生じた。良好にビア電極とM3を形成できたのは、ルテニウム(Ru)だけだった。

銅(Cu)とコバルト(Co)、ルテニウム(Ru)でそれぞれ、M1とM3を接続するスーパービアを試作した結果。上の表はバリアとライナー、配線の金属と成膜方法。下の写真はEDS装置と電子顕微鏡を併用して観察した断面画像。出典:imec(IEDM 2019の発表論文「Three-Layer BEOL Process Integration with Supervia and Self-Aligned-Block Options for the 3nm node」(論文番号19.3)) (クリックで拡大)

銅(Cu)とコバルト(Co)、ルテニウム(Ru)でそれぞれ、M1とM3を接続するスーパービアを試作した結果。上の表はバリアとライナー、配線の金属と成膜方法。下の写真はEDS装置と電子顕微鏡を併用して観察した断面画像。出典:imec(IEDM 2019の発表論文「Three-Layer BEOL Process Integration with Supervia and Self-Aligned-Block Options for the 3nm node」(論文番号19.3)) (クリックで拡大)従来技術の42%にビア抵抗を大きく削減

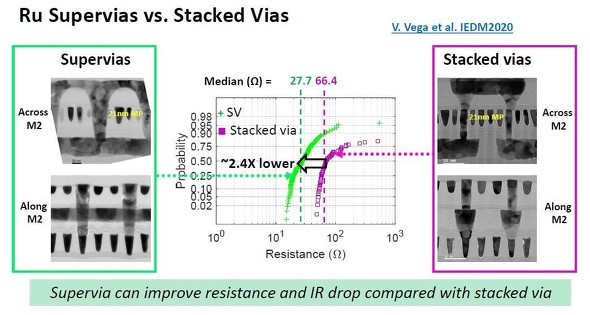

そこでルテニウム(Ru)の多層配線で、M1とM3を接続するビアの電気抵抗を従来技術(スタックビア)とスーパービアで比べてみた。M1とM3は互いに平行な直線群で配線ピッチは36nm、M2はM1(およびM3)と直交する平行直線群で配線ピッチは21nmである。

試作したビアの抵抗値(中央値)は従来技術が66.4Ω、スーパービアが27.7Ωだった。スーパービアの抵抗値は、従来技術の2.4分の1(42%)と大幅に減少した。

スーパービア(左)と従来技術(スタックビア)(右)の抵抗値(測定値)。写真は断面の電子顕微鏡観察像。配線ピッチはM2が21nm、M1とM3が36nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)

スーパービア(左)と従来技術(スタックビア)(右)の抵抗値(測定値)。写真は断面の電子顕微鏡観察像。配線ピッチはM2が21nm、M1とM3が36nm。出典:imec(IEDM2020のチュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials」の配布資料) (クリックで拡大)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

CMOS多層配線の高密度化を支えるビア電極の微細化

CMOS多層配線の高密度化を支えるビア電極の微細化

今回は、多層配線技術の中核を成すビア電極技術について解説する。 高アスペクト比、バリアレス、エアギャップが2nm以降の配線要素技術

高アスペクト比、バリアレス、エアギャップが2nm以降の配線要素技術

今回は、銅配線からルテニウム配線への移行と微細化ロードマップについて紹介する。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 HDD大手SeagateとWDの2021会計年度業績、営業利益が拡大

HDD大手SeagateとWDの2021会計年度業績、営業利益が拡大

米Seagate Technologyと米Western Digitalの、2021会計年度(2021年6月期)の業績を紹介する。 HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

HDD大手Western Digitalの業績、前年同期比の営業利益が3四半期連続で増加

今回は、米Western Digitalの2021会計年度第1四半期の業績を紹介する。 新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

新材料で次々世代を狙う「強誘電体メモリ(FeRAM)」

今回は「強誘電体メモリ(FeRAM)」を取り上げる。FeRAMの記憶原理と、60年以上に及ぶ開発の歴史を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

Special SitePR

あなたにおすすめの記事PR