多層配線のビア抵抗を大幅に低減する「スーパービア」:福田昭のデバイス通信(322) imecが語る3nm以降のCMOS技術(25)(1/2 ページ)

今回は、奇数番号(あるいは偶数番号)で隣接する配線層(2層上あるいは2層下の配線層)を接続するビア電極の抵抗を大幅に下げる技術、「スーパービア(supervia)」について解説する。

2層上下の配線層を接続するビア電極の課題

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

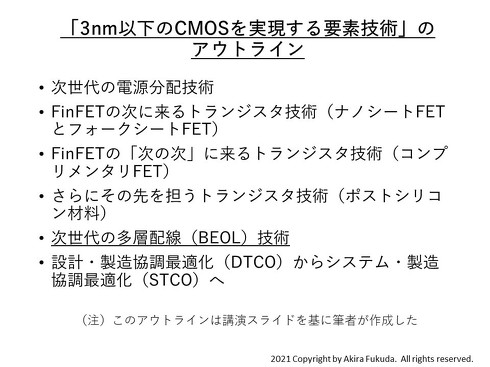

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第21回から、「次世代の多層配線(BEOL)技術」の講演パートを紹介している(クリックで拡大)

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。本シリーズの第21回から、「次世代の多層配線(BEOL)技術」の講演パートを紹介している(クリックで拡大)本シリーズの第21回から、5番目のパートである「次世代の多層配線(BEOL)技術」の講演内容を紹介している。3nm以降の技術世代(技術ノード)を担う多層配線技術を主題とする。前回は、多層配線技術の中核を担う「ビア電極」技術を簡単に解説した。具体的には、3nm以降の技術世代ではビア電極の金属に高融点金属を使う必要があること、奇数番号(あるいは偶数番号)の配線層同士を垂直に接続するビアの重要性が高まっていること、などを説明した。

今回は、奇数番号(あるいは偶数番号)で隣接する配線層(2層上あるいは2層下の配線層)を接続するビア電極の抵抗を大幅に下げる技術、「スーパービア(supervia)」について述べる。

従来、奇数番号(あるいは偶数番号)で隣接する配線層を垂直に接続するビア電極には「スタックビア(Stacked Via)」と呼ぶ技術が使われてきた。例えば第1層金属配線(M1)と第3層金属配線(M3)を結ぶビア電極を想定しよう。スタックビア技術では、M1と第2層金属配線(M2)を接続するビア(V1)を初めに製造し、次にM2を作成する。それから、M2とM3を接続するビアを製造する。最後にM3を成膜する。

スタックビアの弱点は、M1とM3を接続する電気抵抗が、M1とM2(あるいはM2とM3)を接続するビアの電気抵抗に比べると高くなることと、ビアの製造工程が複雑になることだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長