「InFO」技術を低コストの高性能コンピューティング(HPC)に応用:福田昭のデバイス通信(331) TSMCが開発してきた最先端パッケージング技術(4)(1/2 ページ)

今回はInFOを高性能コンピューティング(HPC)向けに改良した「InFO_oS(InFO-on-Substrate)」を説明する。

小型薄型パッケージング技術「InFO」をHPC向けに改良

高性能プロセッサとその関連技術に関する国際学会「Hot Chips」がことし(2021年)8月22日〜24日にオンラインで開催された。「Hot Chips」は高性能プロセッサの最新技術情報を入手できる貴重な機会として知られている。会期は3日間で、初日が「チュートリアル(Tutorials)」と呼ぶ技術講座、2日目と3日目が「カンファレンス(Conference)」と呼ぶ技術講演会となっており、講演会とは別にポスター発表の機会も用意される。オンライン開催となったことしは、あらかじめ録画されたビデオをプログラムに沿って公開する形式となった。参加登録者は開催後も一定の期間は、オンデマンドで講演を聴講できる。

初日の「チュートリアル(Tutorials)」では、13件の講演が実施された。その中で「先進パッケージング技術」に関する講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」が極めて興味深かった。講演者はTSMCで研究開発担当バイスプレジデント(現在はシステム集積化手法開発担当バイスプレジデント)をつとめるDouglas Yu氏である。

そこで本講演の概要を第328回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

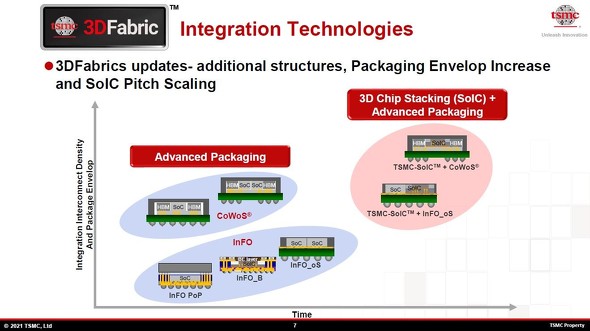

講演「TSMC packaging technologies for chiplets and 3D(チップレットと3次元集積に向けたTSMCのパッケージング技術)」のアウトライン[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)前回では前半に、TSMCが開発してきた先進パッケージング技術のトレンドを展望した。TSMCが過去に開発した先進パッケージング技術は、高性能コンピューティング向けパッケージング技術「CoWoS(Chip on Wafer on Substrate、コワース)」と、モバイル向けパッケージング技術「InFO(Integrated Fan-Out、インフォ)」に大きく分かれる。

前回の後半では、モバイル向けInFOの派生品である「InFO_B(Bottom Only)」を解説した。今回はInFOを高性能コンピューティング(HPC)向けに改良した「InFO_oS(InFO-on-Substrate)」を説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略