EE Times Japan >

LSI >

「InFO」技術を低コストの高性能コンピューティング(HPC)に応用:福田昭のデバイス通信(331) TSMCが開発してきた最先端パッケージング技術(4)(2/2 ページ)

» 2021年10月29日 11時30分 公開

[福田昭,EE Times Japan]

ネットワークスイッチのモジュールに応用

TSMCは高性能コンピューティング(HPC)向けに「CoWoS」を開発し、10年を超える量産実績を有する。CoWoSは高速・高周波信号に対応した優れたパッケージング技術だが、1つだけ大きな弱点がある。中間基板(インターポーザ)に巨大なシリコン基板を使うので、製造コストが高くつくことだ。

モバイル向けのパッケージング技術として開発されたInFOには、パッケージ基板がない。このため製造コストが低い。そこでInFOをベースに、マルチチップ(あるいはチップレット)の搭載を前提にパッケージ基板を追加することでHPC対応を図ったのが、「InFO_oS」である。CoWoSの廉価版ともみなせる。

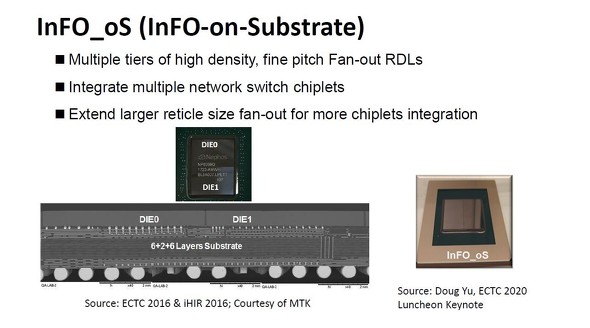

「InFO_oS」の開発例(初代品と思われる)。左上はパッケージを上から見たところ。2枚のシリコンダイ(チップレット)をまとめたネットワークスイッチ。左下は断面構造の観察像。右はネットワークスイッチ・モジュールの全体像[クリックで拡大] 出所:TSMC(2020年12月に開催された国際学会IEDMのショートコース「Advanced 3D System Integration Technologies」のスライドから)

「InFO_oS」の開発例(初代品と思われる)。左上はパッケージを上から見たところ。2枚のシリコンダイ(チップレット)をまとめたネットワークスイッチ。左下は断面構造の観察像。右はネットワークスイッチ・モジュールの全体像[クリックで拡大] 出所:TSMC(2020年12月に開催された国際学会IEDMのショートコース「Advanced 3D System Integration Technologies」のスライドから) 「InFO_oS」の概要と構造図。複数のシリコンダイと基板の間を再配線層(RDL)で結ぶ。RDLの配線幅/間隔は最短で2/2μmと細い。RDLの層数は5層。基板とRDLの間は130μmピッチの銅(Cu)バンプで接続する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「InFO_oS」の概要と構造図。複数のシリコンダイと基板の間を再配線層(RDL)で結ぶ。RDLの配線幅/間隔は最短で2/2μmと細い。RDLの層数は5層。基板とRDLの間は130μmピッチの銅(Cu)バンプで接続する[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)InFO_oSの初代品は2018年に量産を開始した。RDL部分の面積は最大でレチクルの1.5倍(1287mm2前後)とかなり大きい。ネットワークスイッチのモジュールとみられる。第2世代品は10枚のチップレットを搭載したモジュールとなる。ロジックのミニダイが2枚、入出力(IO)のミニダイが8枚という構成である。RDL部分の面積はレチクルの2.5倍(51mm×42mm)と巨大化する。基板の大きさは110mm角。2021年の年内には、第2世代品の量産が始まるとみられる。

「InFO_oS」(ネットワークスイッチ向けモジュール)の開発ロードマップ。横軸はネットワークスイッチの性能。縦軸はモジュールの大きさと消費電力[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)

「InFO_oS」(ネットワークスイッチ向けモジュール)の開発ロードマップ。横軸はネットワークスイッチの性能。縦軸はモジュールの大きさと消費電力[クリックで拡大] 出所:TSMC(Hot Chips 33の講演「TSMC packaging technologies for chiplets and 3D」のスライドから)(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

「システム・製造協調最適化(STCO)」の実現技術(前編)

「システム・製造協調最適化(STCO)」の実現技術(前編)

7nm以降の技術ノードでは、「設計・製造協調最適化(DTCO)」だけでなく、「システム・製造協調最適化(STCO:System Technology Co-Optimization)」も利用することでPPAあるいはPPACのバランスを調整することが求められるようになってきた。 「システム・製造協調最適化(STCO)」の実現技術(後編)

「システム・製造協調最適化(STCO)」の実現技術(後編)

本シリーズの最終回となる今回は、前回に続き「システム・製造協調最適化(STCO)」を解説する。 欧州が欧州半導体法「European Chips Act」の策定へ

欧州が欧州半導体法「European Chips Act」の策定へ

欧州委員会委員長であるUrsula von der Leyen氏が2021年9月15日(現地時間)、一般教書演説の中で、「European Chips Act(欧州半導体法)」の策定に関する発表を行った。中国政府が半導体イノベーションに数十億米ドル規模の資金を投じていることや、米国議会が半導体の戦略的価値について合意に達したことなどを受け、EUは、主体的な最先端技術の実現を目指す法案を策定し、競争に参入していく考えを表明した。 第4世代R-Car SoCも発表、ルネサスが語る車載戦略

第4世代R-Car SoCも発表、ルネサスが語る車載戦略

ルネサス エレクトロニクスは2021年10月6日、オンラインで記者説明会を実施。同社オートモーティブソリューション事業本部の事業本部長、片岡健氏が車載事業戦略について語った。 埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

埋め込みDRAMが大容量キャッシュの製造コスト低減に貢献

今回はDRAMをロジックLSIに埋め込む技術「eDRAM」の製品化事例を解説する。 前進し続けるIntel

前進し続けるIntel

Intelは2021年1月21日(米国時間)、業績発表を行った。それを見ると、同社の“終末時計”のカウントダウンに、少なくとも数秒は追加されたといえるだろう。ただし、完全に楽観視できるわけではなさそうだ。スピンドクター(情報操作が得意な人)たちは、Intelの2020年の業績のマイナス面だけを簡単に強調することができる。また、プラス面よりも欠点の方に反応を示す投資家たちもいる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- Cerebrasが上場 NVIDIA対抗馬の「試金石」となるか

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

Special SitePR

あなたにおすすめの記事PR