AMDが開発した第4世代「EPYC」プロセッサのメモリ構成:福田昭のデバイス通信(375)(2/2 ページ)

CPUコア内蔵ダイとメモリチャンネルを最大4つのグループに分割

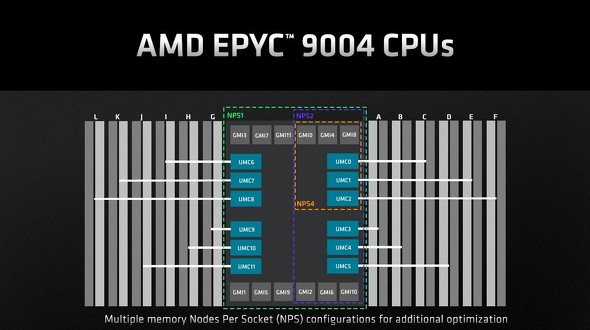

また第4世代EPYCでは、CPUコアとメモリチャンネルをグループ化することでメモリアクセスを最適化するオプション「NPS(Nodes Per Socket)」を備える。NPSには1、2、4のオプションがある。NPS1はグループ化していない状態で、CPUコアを内蔵するダイ(CCD)とメモリチャンネルを自由に接続する。

NPS2は2つのグループに分けた状態である。12枚のCCDと12チャンネルのメモリを2つに分ける。入出力ダイのメモリチャンネルは6チャンネルずつ左右に分かれているので、左の6チャンネルに近い6枚のCCDで1つのグループを、右の6チャンネルに近い6枚のCCDでもう一つのグループを構成する。こうするとCCDからメモリコントローラーまでの平均的な距離が縮まり、信号伝送の遅延時間が短くなるとともに遅延のばらつきも減少する。

さらにNPS4では、物理的な距離の近い3枚のCCDと3つのメモリチャンネルでグループを作る。信号伝送の平均的な遅延時間がさらに短くなり、遅延のばらつきが減る。この結果、メモリアクセスの実効的な高速化に寄与する。

CPUコアとメモリチャンネルをグループ化する「NPS(Nodes Per Socket)」。CPUコア搭載ダイ(CCD)とIODを接続する12個の「GMI(Global Memory Interconnect)」コントローラーと、12個のメモリコントローラー「UMC(Universal Memory Controller)」を、物理的な距離の長短によって最大で4つのグループに分ける。「NPS4」だと、距離の近い3つのGMIと3つのUMCが一つのグループを作る[クリックで拡大] 出所:AMD

CPUコアとメモリチャンネルをグループ化する「NPS(Nodes Per Socket)」。CPUコア搭載ダイ(CCD)とIODを接続する12個の「GMI(Global Memory Interconnect)」コントローラーと、12個のメモリコントローラー「UMC(Universal Memory Controller)」を、物理的な距離の長短によって最大で4つのグループに分ける。「NPS4」だと、距離の近い3つのGMIと3つのUMCが一つのグループを作る[クリックで拡大] 出所:AMD主記憶(メインメモリ)の帯域幅は前世代の2.3倍に拡大

AMDは第4世代EPYCの主記憶性能を、第3世代EPYCと比較した結果も示した。主記憶の帯域幅は平均で356Gバイト/秒に達する。第3世代EPYCの2.3倍と広い。シングルランクとデュアルランクの帯域幅の違いは、平均で4.5%と大きく縮まった。第3世代EPYCのDIMMでは平均で25%の性能差があった。

またメモリアクセスのレイテンシ(遅延時間)は、集積規模が拡大したにもかかわらず、第3世代EPYCと比べて13ナノ秒前後(12%前後)の増加で済んだ。

第4世代EPYCの主記憶性能と、第3世代EPYCの主記憶性能の比較。上から「データ転送速度(帯域幅)」「シングルランクとデュアルランクの帯域幅の違い」「アクセス遅延(レイテンシ)の違い」[クリックで拡大] 出所:AMD

第4世代EPYCの主記憶性能と、第3世代EPYCの主記憶性能の比較。上から「データ転送速度(帯域幅)」「シングルランクとデュアルランクの帯域幅の違い」「アクセス遅延(レイテンシ)の違い」[クリックで拡大] 出所:AMD⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMD、サーバ向け高性能プロセッサ「第4世代EPYC」の第1弾を発表

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコで新製品発表会「together we advance_data centers」を開催し、サーバ向けプロセッサの新製品「EPYC 9004シリーズ」の販売を開始した。 HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

HDD大手Western Digitalの業績、フラッシュの値下がりで営業利益が前年の3分の1に減少

米Western Digitalの「2023会計年度第1四半期」(2022年7月〜9月)を紹介する。 携帯型MP3プレーヤーの黎明期(1997年〜1998年)

携帯型MP3プレーヤーの黎明期(1997年〜1998年)

今回はフラッシュメモリを記憶媒体とする携帯型デジタルオーディオプレーヤー(DAP:Digital Audio Player)を扱う。時期は1997年〜1998年である。 ワイヤレス電力伝送で実際に電子機器を動作させる

ワイヤレス電力伝送で実際に電子機器を動作させる

今回は「7.4 試作例」の講演パートを解説する。ワイヤレス受電端末を試作し、低消費電力の小型機器をワイヤレス電力伝送で動かした。 ワイヤレス受電用端末の試作に向けたアンテナの設計作業

ワイヤレス受電用端末の試作に向けたアンテナの設計作業

今回は「7.2 アンテナ」と「7.3 アンテナの集積化」の内容について、簡単に解説する。 ワイヤレス電力伝送の過去から未来までを展望

ワイヤレス電力伝送の過去から未来までを展望

今回から、「IEDM 2021」でオランダimec Holst Centreでシニアリサーチャー、オランダEindhoven University of TechnologyでフルプロフェッサーをつとめるHubregt J. Visser氏が講演した「Practical Implementation of Wireless Power Transfer(ワイヤレス電力伝送の実用的な実装)」の内容を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待