AMDが開発した第4世代EPYCプロセッサのCXLメモリ拡張:福田昭のデバイス通信(376)(1/2 ページ)

今回は、CXL(Compute Express Link)インタフェースを通じてメモリを拡張する仕組みを説明する。

128レーンのPCIe Gen5インタフェースを複数の用途に活用

AMDは2022年11月10日(米国時間)に米国カリフォルニア州サンフランシスコでサーバ向けプロセッサ「EPYC(エピック)」の新製品発表会「together we advance_data centers」を開催した。新しい「EPYC」は、x86互換の64ビットCPUコア「Zen(ゼン)」シリーズの第4世代となる最新のCPUコア「Zen4」を搭載する。名称は「第4世代(4th Gen)EPYC」である。

そこで本コラムの第371回から、第4世代EPYCプロセッサとZen4コアの内容をご説明してきた。前回は、第4世代EPYCプロセッサのメインメモリ(主記憶)を解説した。今回は、CXL(Compute Express Link)インタフェースを通じてメモリを拡張する仕組みをご説明する。

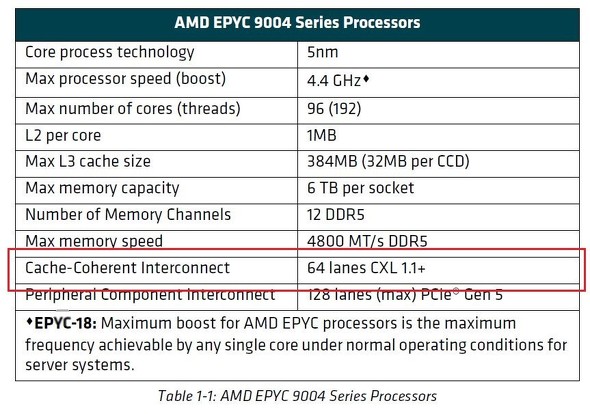

第4世代EPYCプロセッサ「EPYC 9004シリーズ」の概要。赤枠で囲んだ部分がCXLインタフェースによる拡張記憶の項目[クリックで拡大] 出所:AMD、「AMD EPYC 9004 Series Architecture Overview」、Nov. 2022.

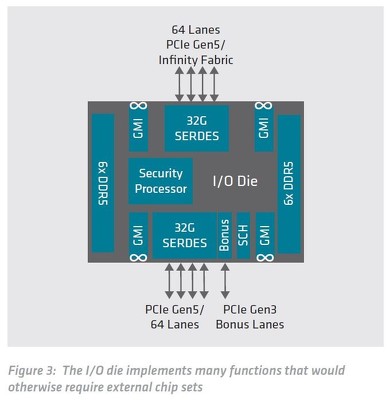

第4世代EPYCプロセッサ「EPYC 9004シリーズ」の概要。赤枠で囲んだ部分がCXLインタフェースによる拡張記憶の項目[クリックで拡大] 出所:AMD、「AMD EPYC 9004 Series Architecture Overview」、Nov. 2022.第4世代EPYCの最初の製品である「EPYC 9004シリーズ」は、本コラムの第372回で述べたように、Zen4コアを内蔵する「Core Complex Die(CCD)」と、メモリや入出力、セキュリティなどを担う「IO Die(IOD)」で構成されている。IODは2×6チャンネルのDDR5メモリコントローラーや8×16ビットの入出力インタフェース、CCDと接続する4×3チャンネルのGMI(Global Memory Interface)、セキュリティプロセッサなどを内蔵する。

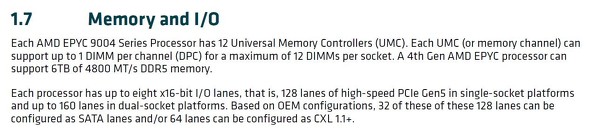

これらの回路ブロックの中で、8×16ビットの入出力インタフェースは物理(電気)的には第5世代PCI Express(PCIe Gen5)である。128レーンのPCIe Gen5が「ベース」として存在する。「ベース」と記述したのは、用途によって適切な通信プロトコルを載せたインタフェースに変更できるからだ。

例えば2ソケット(2プロセッサ)構成のときには、128レーンのPCIe Gen5からプロセッサ間の相互接続(Infinity Fabric)リンクを割り当てる。割り当て可能なレーン数は3×16ビット(48レーン)あるいは4×16ビット(64レーン)である。

一部をSATAインタフェースに割り当てることも可能だ。最大で32レーンをSATAコントローラーとして利用できる。

そしてCXL(Compute Express Link)インタフェースには、最大で64レーンのPCIe Gen5を割り当てられる。サポートするCXLのバージョンは「1.1+」、サポートするCXLデバイスのタイプは「タイプ3(「メモリバッファ(メモリエキスパンダ)」)」である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増