光インターコネクトの新しい指標:光伝送技術を知る(23) 光伝送技術の新しい潮流と動向(4)(2/3 ページ)

Shoreline Density(Gbit/s/mm)

インターコネクトFOMでは、Gbit/s/mmという、電気配線で使用されているが光ではなじみが薄い指標が分子に来ている。Shoreline Bandwidth Density(単にShoreline Density)あるいはBeach Front Bandwidth Densityという。二次元的な配線基板等に境界線を定義し、そこを通過可能な全信号容量を境界線長で割った指標で、パッケージやPCB実装などにおける電気配線技術の指標の一つである。光インターコネクトが電気配線を置き換えることを目的とするならば当然の指標であろう。ただし、片方向か両方向かによって数字が2倍違うので注意が必要だが、ここでは両方向あるいは全二重で検討した。

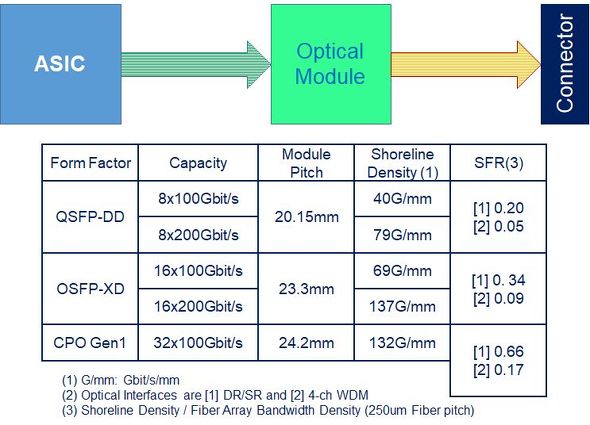

図2に、代表的な高速光モジュール、QSFP-DD[1]、OSFP-XD[2]とOIF 3.2T CPO[3]のShoreline Densityを示す。光インターコネクトへの期待値として数100Gbit/s/mmという数字が多い。図2から、3.2Tにおいて100Gbit/s/mmを超えることが分かる。また、ファイバアレイが伝送媒体であるので、ファイバアレイの全伝送容量をアレイ幅(ファイバピッチ×本数)で割った値に対する比も重要だと考えており、図2の表に加えた。

図2から、モジュールの幅は20〜24mmとあまり差がないので、Shoreline Densityは電気ピン数増加(8→16→32)によるモジュール容量の増加によって向上していることが分かる。つまり、高密度電気ピンが必要である。また、4チャネル多重化でファイバアレイ伝送密度(Gbit/s/mm)は向上するが、モジュールを、多重化を前提に定義することでShoreline Densityのさらなる向上が期待できる。図2の表のSFRは「1」に近づけることが求められているのだ。

[1] "QSFP-DD/QSFP-DD800/QSFP112 Hardware Specification for QSFP DOUBLE DENSITY 8X AND QSFP 4X PLUGGABLE TRANSCEIVERS," Revision 6.3, July 26, 2022

[2] “OSFP-XD, OCTAL SMALL FORM FACTOR eXtra Dense PLUGGABLE MODULE” Rev 1.0, March 17th, 2023

[3] “OIF-Co-Packaging-3.2T-Module-01.0,” March 29, 2023

右から左にデータを流す光インターコネクトではShoreline Densityはモジュールの搭載ピッチで決まる。搭載ピッチはモジュールの幅に加え、固定方式、放熱方式などHost Board実装が影響する。しかし、ここではモジュール幅に注目して考察したい。

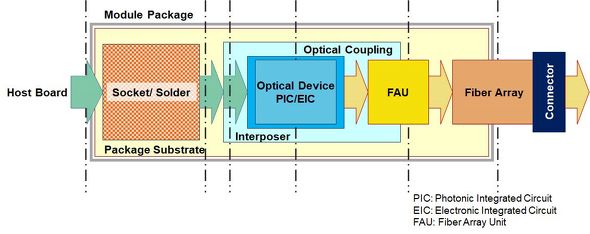

図3に光インターコネクトの主要部品と信号の流れを示す。分かりやすいように送信のみを示したが、受信部では、信号の流れが図3とは反対になる。電気と光の接続ピッチ変換としてのInterposerやFiber Array Unit(FAU)は無い場合もあるだろう。それぞれの部品境界線上でShoreline Densityが要求仕様を満たすようにしなければならない。

Broadcomは、光通信の学会「OFC」のパネルなどで、“Pitch Matched”を発表している。アレイ部を全て同じピッチで設計することにより、実装が容易になり、チャネル間差の低減にもつながり、安定性が期待できる。ファイバーアレイピッチを基本に、各アレイ部を設計することが王道であると考えている。

それぞれの部品の課題を考察してみよう。ここではファイバーアレイ単体の幅をイメージする。250μmピッチの標準ファイバーの16本、32本と64本のアレイは、それぞれ4mm、8mmと16mmである。

電気信号の入出力部では、光インターコネクト固有の課題として交換容易性の要求がある。故障率がASICなどに比べ比較的高いことから、故障時に交換可能なこと、特にデータセンターなどのフィールドで交換できることが要求されている。OIF 3.2T CPOでは幅方向に0.6mmピッチのLGAソケットが採用された。規格化において0.4mmピッチや0.45mmピッチなどの提案・議論があった。ソケットに関しては実用的な標準化が重要であるが、Shoreline Densityの観点から決定する必要がある。ソケットの挿入のサポートやロック機構なども幅が広がらない方式が好ましい。

Photonic/Electronic Integrated Circuit(PIC/EIC)ではアレイのピッチ・マッチとともにアレイ部以外の幅を拡張する要因の最小化が課題でもある。バイアス回路やパッドなどの配置、InterposerやPackage Substrateの幅など「広げない」チップ設計・実装も重要である。また、ワイヤボンディングよりチップ内にパッドを配置できるフリップチップボンディング、(マイクロ)ソルダーバンプボンディングあるいはメタルダイレクトボンディングなどが有利になる。

FAUやファイバーの固定ではケーブル化に伴う外被や勘合ピン(穴、溝)、機械的あるいは温度変化によるストレス対策構造など幅拡張の要因が多い。レセプタクル(Receptacle)やDetachable Connecterを用いる場合は部品固定方式には注意が必要である。IntelのOptical Bridge(FAUの一種)のようにSi-photonicsの1次元アレイ入出力から3次元の光導波路を用いて2段アレイに配置変換し、FAU部のアレイ幅を半減する方式もある[4]。

[4] N. Psaila, et al, “Detachable Optical Chiplet Connector for Co-packaged Photonics,” JLT, 2023.

以上から、Shoreline Densityを確保するには実装技術が重要であることが分かる。当面は200Gbit/s/mmが目標になると考えているが、それに向かったデバイスや実装技術の開発が急務である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- キオクシア25年度 驚異の決算 Q4純利益は前年比30倍

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- iPhone好調で過去最高も、「世界一」維持へ動くソニー半導体

- 加賀電子が新光商事にTOB、完全子会社化へ

- 「技術ナンバーワンであり続ける」 ソニーセミコンCTOが語る技術戦略

- SiC LSIの事業化に挑む 28年以降ADCのサンプル出荷へ

- AIの「トンデモ判断」で本番DBが全飛び! 他山の石にしたいAIコーディングの落とし穴

- サンケン電気26年3月期は赤字転落 中国の「自前主義」響く

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk