「半導体業界の巨人」3社がCFETに照準 製造では課題が山積も:Intel、Samsung、TSMC(1/2 ページ)

専門家たちが米国EE Timesに語ったところによると、IntelとSamsung Electronics(以下、Samsung)、TSMCは、現在の最先端のナノシート技術において引き続き生じているスケーリングの問題を解決すると期待される、新しい3D(3次元)チップアーキテクチャの開発に本腰を入れ始めているという。

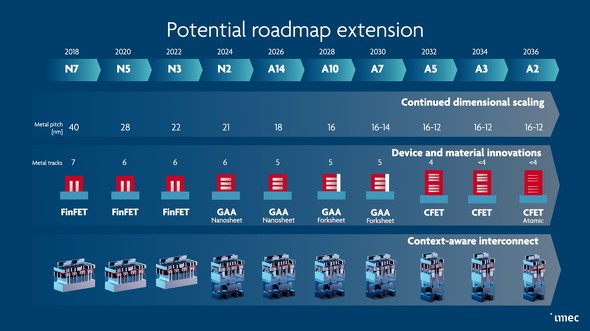

ベルギーの研究開発機関imecでCMOSデバイスプログラム担当ディレクターを務めるNaoto Horiguchi氏によると、これら最大手3社は、米国カリフォルニア州サンフランシスコで2023年12月9〜13日(現地時間)に開催された半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」において、初めてプレゼンテーションを行い、今後10年間でCFET(コンプリメンタリFET)アーキテクチャの商用化を実現する予定であることを明かした。CFETは、PMOSとNMOSをシリコン表面に対して垂直に積層するもの。

Horiguchi氏は、「IntelとSamsung、TSMCはいずれも、最新の達成成果を披露した。3社が同じセッションの中で成果を発表したのは、初めてのことである。一段と本腰を入れているようだ」と述べている。

imecは、「半導体業界は、CFETの時代が到来する前に、3世代にわたるナノシートアーキテクチャと、微細化が停止してしまったSRAMなどのCMOSコンポーネントに関連する問題に耐えなければならないだろう。微細化が停止すれば、HPC(高性能コンピューティング)向けチップの設計者たちは、レガシーの技術ノードやチップレットを組み合わせるという回避策を取ることで、SRAMなどのCMOS機能のディスアグリゲーション(分離)を余儀なくされることになる」と述べている。imecがCFETの概念を提唱したのは2016年ごろのことだ。

Horiguchi氏は、「アナログやI/Oのような一部のレガシー技術は、異なるスキームで統合しなければならないだろう。例えば、チップレット技術を使用してアナログやI/Oを統合する方法などが挙げられる。少なくとも一部のロジックやSRAMは、CFETアーキテクチャを使うことでスケーリングが可能だ。これが、われわれが現在期待していることである」と付け加えた。

プロセスの微細化は2032年までに鈍化か

imecの予測では、プロセスノードの微細化の速度は2032年までには鈍化し、チップレットや高性能パッケージングを、微細化を継続できる高性能ロジックコンポーネントとうまく組み合わせて使用することに、依存せざるを得なくなっていく見込みだという。

Horiguchi氏は、「CMOSデバイスをナノシートだけでスケーリングすることは非常に難しい。CFETでは、デバイススケーリングを本格的に継続し、それをチップレットや高性能パッケージングなどの他の技術と組み合わせて、チップ性能を高めることが可能だ。CFETは、継続的なデバイススケーリングの実現に向けた道を切り開いていく。これが、CFETのセールスポイントだ」と述べている。

imecは、「CFETは2032年までに、1nmノードを超えるデバイスアーキテクチャを採用する見込みだ」と述べる。Samsungは2022年に、業界で初めて3nmノードでナノシート/GAA(Gate-All-Around)アーキテクチャを導入した。またTSMCは、2025年に2nmノードでナノシートを導入する予定だとしている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」